一 實驗內容簡要描述

1.實驗目的

學會驅動程序的編寫方法,配置S3C2410的LCD驅動,以及在LCD屏上顯示包括bmp和jpeg兩種格式的圖片

2.實驗內容

(1)分析S3c2410實驗箱LCD以及LCD控制器的硬體原理,據此找出相應的硬體設置參數,參考xcale實驗箱關於lcd的設置,完成s3c2410實驗箱LCD的設置

(2)在LCD上顯示一張BMP圖片或JPEG圖片

3.實驗條件(軟硬體環境)

PC機、S3C2410開發板、PXA255開發板

二 實驗原理

1. S3C2410內置LCD控制器分析

1.1 S3C2410 LCD控制器

一塊LCD屏顯示圖像,不但需要LCD驅動器,還需要有相應的LCD控制器。通常LCD驅動器會以COF/COG的形式與LCD 玻璃基板製作在一起,而LCD控制器則由外部電路來實現。而S3C2410內部已經集成了LCD控制器,因此可以很方便地去控制各種類型的LCD屏,例如:STN和TFT屏。S3C2410 LCD控制器的特性如下:

(1)STN屏

支持3種掃描方式:4bit單掃、4位雙掃和8位單掃

支持單色、4級灰度和16級灰度屏

支持256色和4096色彩色STN屏(CSTN)

支持分辯率為640*480、320*240、160*160以及其它規格的多種LCD

(2)TFT屏

支持單色、4級灰度、256色的調色板顯示模式

支持64K和16M色非調色板顯示模式

支持分辯率為640*480,320*240及其它多種規格的LCD

對於控制TFT屏來說,除了要給它送視頻資料(VD[23:0])以外,還有以下一些信號是必不可少的,分別是:

VSYNC(VFRAME) :幀同步信號

HSYNC(VLINE) :行同步信號

VCLK :像數時鐘信號

VDEN(VM) :數據有效標誌信號

由於本項目所用的S3C2410上的LCD是TFT屏,並且TFT屏將是今後應用的主流,因此接下來,重點圍繞TFT屏的控制來進行。

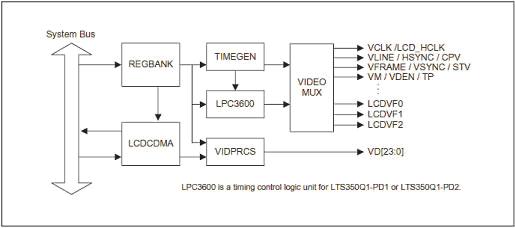

圖1.1是S3C2410內部的LCD控制器的邏輯示意圖:

圖1.1

REGBANK 是LCD控制器的寄存器組,用來對LCD控制器的各項參數進行設置。而 LCDCDMA 則是LCD控制器專用的DMA通道,負責將視頻資料從系統匯流排(System Bus)上取來,通過 VIDPRCS 從VD[23:0]發送給LCD屏。同時 TIMEGEN 和 LPC3600 負責產生 LCD屏所需要的控制時序,例如VSYNC、HSYNC、VCLK、VDEN,然後從 VIDEO MUX 送給LCD屏。

1.2 TFT屏時序分析

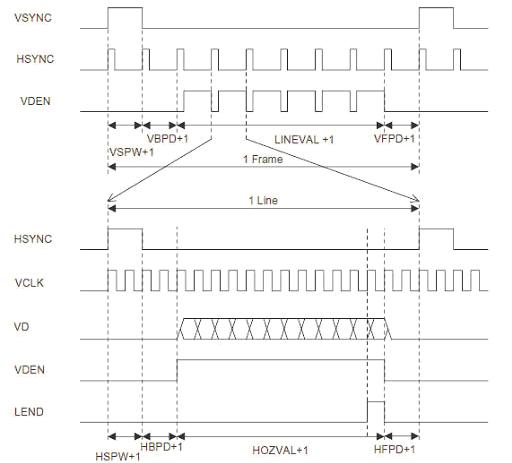

圖1.2是TFT屏的典型時序。其中VSYNC是幀同步信號,VSYNC每發出1個脈衝,都意味著新的1屏視頻資料開始發送。而HSYNC為行同步信號,每個HSYNC脈衝都表明新的1行視頻資料開始發送。而VDEN則用來標明視頻資料的有效,VCLK是用來鎖存視頻資料的像數時鐘。

並且在幀同步以及行同步的頭尾都必須留有回掃時間,例如對於VSYNC來說前回掃時間就是(VSPW+1)+(VBPD+1),后回掃時間就是(VFPD +1);HSYNC亦類同。這樣的時序要求是當初CRT顯示器由於電子槍偏轉需要時間,但後來成了實際上的工業標準,乃至於後來出現的TFT屏為了在時序上於CRT兼容,也採用了這樣的控制時序。

圖1.2

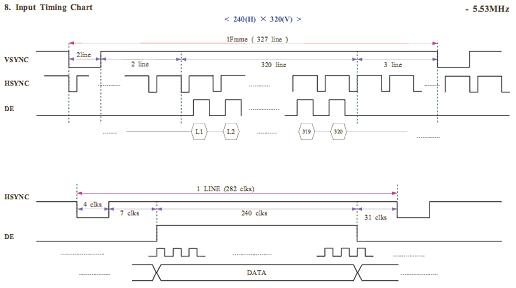

S3C2410實驗箱上的LCD是一款3.5寸TFT真彩LCD屏,分辯率為240*320,下圖為該屏的時序要求。

圖1.3

通過對比圖1.2和圖1.3,我們不難看出:

VSPW+1=2 -> VSPW=1

VBPD+1=2 -> VBPD=1

LINVAL+1=320-> LINVAL=319

VFPD+1=3 -> VFPD=2

HSPW+1=4 -> HSPW=3

HBPD+1=7 -> HBPW=6

HOZVAL+1=240-> HOZVAL=239

HFPD+1=31 -> HFPD=30

以上各參數,除了LINVAL和HOZVAL直接和屏的分辯率有關,其它的參數在實際操作過程中應以上面的為參考,不應偏差太多。

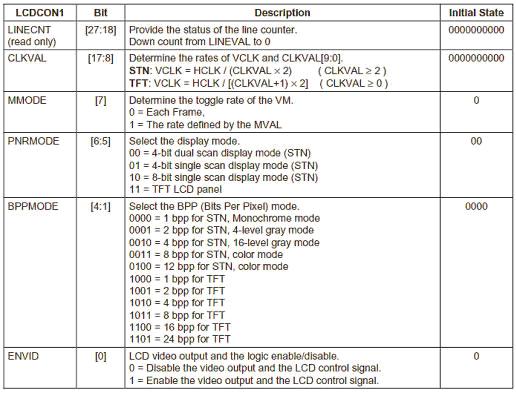

1.3 LCD控制器主要寄存器功能詳解

圖1.4

LINECNT :當前行掃描計數器值,標明當前掃描到了多少行。

CLKVAL :決定VCLK的分頻比。LCD控制器輸出的VCLK是直接由系統匯流排(AHB)的工作頻率HCLK直接分頻得到的。做為240*320的TFT屏,應保證得出的VCLK在5~10MHz之間。

MMODE :VM信號的觸發模式(僅對STN屏有效,對TFT屏無意義)。

PNRMODE :選擇當前的顯示模式,對於TFT屏而言,應選擇[11],即TFT LCD panel。

BPPMODE :選擇色彩模式,對於真彩顯示而言,選擇16bpp(64K色)即可滿足要求。

ENVID :使能LCD信號輸出。

圖1.5

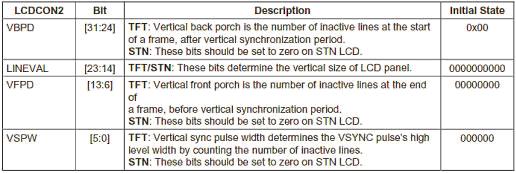

VBPD , LINEVAL , VFPD , VSPW 的各項含義已經在前面的時序圖中得到體現。

圖1.6

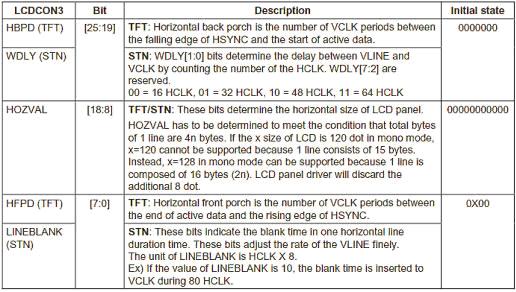

HBPD , HOZVAL , HFPD 的各項含義已經在前面的時序圖中得到體現。

圖1.7

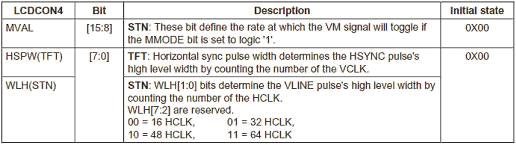

HSPW 的含義已經在前面的時序圖中得到體現。

MVAL 只對 STN屏有效,對TFT屏無意義。

HSPW 的含義已經在前面的時序圖中得到體現,這裡不再贅述。

MVAL 只對 STN屏有效,對TFT屏無意義。

圖1.8

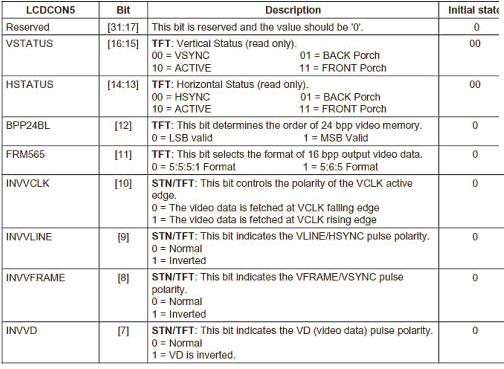

VSTATUS :當前VSYNC信號掃描狀態,指明當前VSYNC同步信號處於何種掃描階段。

HSTATUS :當前HSYNC信號掃描狀態,指明當前HSYNC同步信號處於何種掃描階段。

BPP24BL :設定24bpp顯示模式時,視頻資料在顯示緩衝區中的排列順序(即低位有效還是高位有效)。對於16bpp的64K色顯示模式,該設置位無意義。

FRM565 :對於16bpp顯示模式,有2中形式,一種是RGB=5:5:5:1,另一種是5:6:5。后一種模式最為常用,它的含義是表示64K種色彩的16bit RGB資料中,紅色(R)佔了5bit,綠色(G)佔了6bit,蘭色(B)佔了5bit

INVVCLK , INVLINE , INVFRAME , INVVD :通過前面的時序圖,我們知道,CPU的LCD控制器輸出的時序默認是正脈衝,而LCD需要VSYNC(VFRAME)、VLINE(HSYNC)均為負脈衝,因此 INVLINE 和 INVFRAME 必須設為“1 ”,即選擇反相輸出。

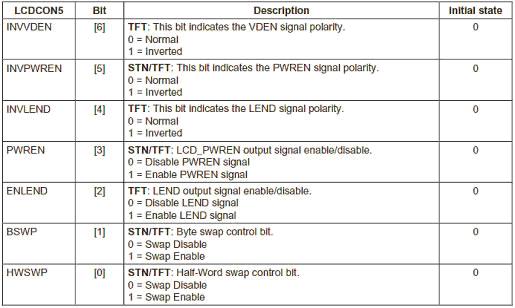

INVVDEN , INVPWREN , INVLEND 的功能同前面的類似。

PWREN 為LCD電源使能控制。在CPU LCD控制器的輸出信號中,有一個電源使能管腳LCD_PWREN,用來做為LCD屏電源的開關信號。

ENLEND 對普通的TFT屏無效,可以不考慮。

BSWP 和 HWSWP 為位元組(Byte)或半字(Half-Word)交換使能。由於不同的GUI對FrameBuffer(顯示緩衝區)的管理不同,必要時需要通過調整 BSWP 和 HWSWP 來適應GUI。

[admin via 研發互助社區 ] S3c2410 LCD驅動學習心得已經有3564次圍觀

http://cocdig.com/docs/show-post-42079.html