用於NMOS的驅動電路

4,輸入和輸出的電流限制 5,通過使用合適的電阻,可以達到很低的功耗。

6,PWM信號反相。NMOS並不需要這個特性,可以通過前置

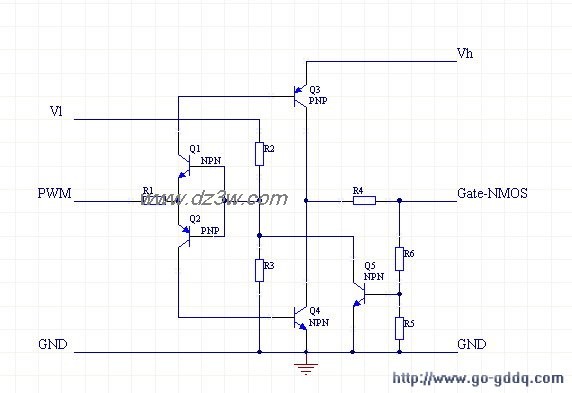

下面對NMOS驅動電路原理做一個簡單分析: Vl和Vh分別是低端和高端的電源,兩個電壓可以是相同的,但是Vl不應該超過Vh。

Q1和Q2組成了一個反置的圖騰柱,用來實現隔離,同時確保兩隻驅動管Q3和Q4不會同時導通。

R2和R3提供了PWM電壓基準,通過改變這個基準,可以讓電路工作在PWM信號波形比較陡直的位置。

Q3和Q4用來提供驅動電流,由於導通的時候,Q3和Q4相對Vh和GND最低都只有一個Vce的壓降,這個壓降通常只有0.3V左右,大大低於0.7V的Vce。

R5和R6是反饋電阻,用於對gate電壓進行採樣,採樣后的電壓通過Q5對Q1和Q2的基極產生一個強烈的負反饋,從而把gate電壓限制在一個有限的數值。這個數值可以通過R5和R6來調節。

最後,R1提供了對Q3和Q4的基極電流限制,R4提供了對MOS管的gate電流限制,也就是Q3和Q4的ICe的限制。必要的時候可以在R4上面並聯加速電容。

[admin via 研發互助社區 ] 用於NMOS的驅動電路已經有2033次圍觀

http://cocdig.com/docs/show-post-25701.html