現場可編程門陣列(FPGA,Field Programmable Gate Array)是一種高密度可編程邏輯器件,其邏輯功能是通過把設計生成的數據文件配置進晶元內部的靜態配置數據存儲器(SRAM )來實現的,具有可重複編程性,可以靈活實現各種邏輯功能。由於FPGA器件採用的是SRAM 工藝,在斷電的情況下FPGA內的配置數據將丟失。所以,在典型的採用FPGA器件的電子系統中通常將FPGA 的配置數據存放於其兼容的SPROM 中,上電時由控制電路將SPROM中的配置數據裝入FPGA器件中。但是通常的SPROM價格昂貴,且是一次性,不利於FPGA程序的更新,所以有必要分析FPGA 的配置原理,採用廉價、能重複使用的方式配置FPGA。

本文主要根據Altera公司手冊及以前的經驗,設計和完成了一種新的FPGA配置文件下載更新的方法。其主要原理是在每次啟動系統時,由配置控制器從Flash中讀出FPGA配置文件,再下載到FPGA中以完成器件的配置功能。當系統需要升級更新FPGA配置文件時,可通過網路或者由主機通過JTAG(Joint Test Action Group)介面(未聯網時)將配置文件發送給基於Nios II處理器的嵌入式系統中,由Nios II處理器更新系統中的Flash。當Flash內容更新后,系統就可實現在加電時由配置控制器自動將配置文件下載到FPGA中。而配置控制器是採用複雜可編程邏輯器件(CPLD,Complex Programmable Logic Device),主要功能是實現並串轉換。這樣在不需要任何硬體動作和專業軟體的情況下,只需要進行常規軟體操作就可以更新FPGA的配置文件。不僅節約了成本,還有效地縮小了系統體積,有利於以後系統工程的升級更新。

1 基於Nios II的嵌入式系統簡介

Nios II是Altera公司在第一代軟核處理器Nios的基礎上於2004年5月為其FPGA產品配套開發的軟核CPU。Nios II是一種採用流水線技術、單指令流的基於RISC技術的通用嵌入式軟核處理器、哈佛體系結構,地址、數據、指令均為32位,最高性能可達到200DMIPS (Dhrystones MIPS)。Nios II系統中的外設具有可配置性,用戶可根據實際應用來裁剪,並且Nios II處理器有很好的自定義指令支持,大部分指令均可以在一個時鐘周期內完成,這也是可配置處理器的優勢所在。Nios II在邏輯功能上是32位的精簡指令集CPU;而在實現方式上,它是在FPGA上通過編程方式實現的,這也是與傳統的CPU一個根本差別。Nios II的匯流排方式也採用了一種簡單的匯流排體系結構——Avalon匯流排。該軟核CPU為可編程片上系統SOPC給用戶提供了一套綜合解決方案,它可以與用戶自定義邏輯結合構成SOC系統,並下載到Altera的FPGA 晶元中,使得FPGA在嵌入式系統領域的地位越來越重要。

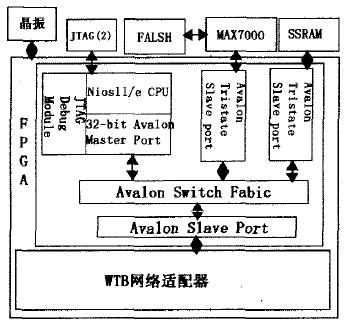

基於Nios II的嵌入式系統主要實現了絞線式列車匯流排(WTB,Wire Train Bus) 網路節點機的功能,該系統是基於SOPC技術,首先定製Nios II的嵌入式CPU、必要的外部和相關配置的晶元,然後按照WTB標準和Nios II特有的Avalon匯流排介面設計並通過VHDL實現MAU的功能,由Nios II來控制WTB網路通信功能。基於Nios II嵌入式軟核WTB網路節點機硬體體系結構主要由FPGA、Flash nemory、SSRAM Memory、MAX7000配置控制器等硬體組成。FPGA 採用Altera公司的Cyclone系列的EP1C6Q240C8,使用Altera公司的MAX7000系列的EPM7256配置控制器完成對EP1C6Q240C8的配置,基於Nios II的嵌入式系統的原理圖如圖1所示。

其中圖中的JTAG2表明有2個JTAG介面,一個用來在線配置調試,一個用來下載更新配置文件。

2 FPGA 器件的配置方式

FPGA的配置方式分為主動方式(AS,Active Serial)、被動方式(PS,Passive Serial)和JTAG方式,數據寬度有8位并行方式和串列方式兩種。在主動模式下,FPGA在上電后,由PLD器件引導配置操作過程,它控制著外部存儲器和初始化過程,自動將配置數據從相應的外存儲器讀入到SRAM 中,實現內部結構映射;而在被動模式下,FPGA則作為從屬器件,由相應的控制電路或微處理器提供配置所需的時序,實現配置數據的下載。

下面對基於ICR(In-Circuit Reconfigurability)FPGA器件的配置方式進行詳細分析:

(1) 主動串列方式(AS,Active Serial):主要使用EPC配置器件,適應用低速設備的配置;

(2) 被動串列方式(PS,Passive Seria1):使用配置控制器的串列介面;

(3) 被動并行同步方式(PPS,Passive Parallel Synchronous):使用配置控制器的并行同步介面;

(4) 被動并行非同步方式(PPA,Passive Parallel Asynchronous):使用配置控制器的并行非同步介面;

(5) 邊界掃描方式(JTAG,Joint Test Action Group):使用JTAG下載電纜。

基於AS方式配置使用EPC配置器件進行配置時,首先將配置文件從計算機下載到EPC配置器件中去,然後由EPC配置器件控制配置時序對FPGA進行配置。EPC配置器件有一次可編程和可擦寫編程型兩種:一次可編程型晶元只能寫入一次,不適於開發階段反覆調試、修改及產品的方便升級;可擦除編程型價格昂貴,且容量有限,對於容量較大的可編程邏輯器件,需要多片配置晶元組成菊花鏈進行配置,增加了系統設計的難度。

使用PS、PPS、PPA方式配置時,配置文件事先是以二進位形式保存在系統ROM 中,然後通過配置控制器將配置數據送進FPGA中。PS是通過串列方式送到FPGA中,PPS是以并行方式送給FPGA。FPGA在其內部將并行數據轉換成串列數據,該數據轉換時需要外部配置時鐘的驅動。比較PS和PPS,所用的配置時間幾乎相同,而PS的介面方式比較簡單,所以嵌入式系統中通常選擇PS方式配置FPGA。使用PPA方式配置數據時,配置控制器將配置數據以并行方式送給FPGA,然後在FPGA內部進行數據串列化處理。與PPS不一樣的地方是串列化處理時不需要配置外部時鐘的驅動,但介面更複雜,工

程中很少使用。

邊界掃描方式需要連接計算機,無法在現場使用,嵌入式系統中很少採用這種方式。

通過上述的分析,在嵌入式系統中要使用FPGA時,可以採用專用EPC配置器件、PS、PPS、PPA和CPLD配置器件,但是PS、PPS、PPA比專用EPC配置更具成本和體積優勢。在PS、PPS、PPA中,PS又是最優的通信方式。所以在嵌入式系統中,選擇利用CPLD配置器件的PS被動串列方式來配置FPGA最為合適。

而本文正是利用CPLD配置控制器基於PS方式進行FPGA配置的新方法,在每次啟動系統時,由配置控制器從Flash中讀出FPGA配置文件的數據信息,再下載到FPGA中以完成器件的配置功能。當系統需要升級更新FPGA配置文件時,可通過網路或者由主機通過JTAG介面(未聯網時)將配置文件發送給基於Nios II處理器的嵌入式系統中,由Nios II處理器更新系統中的Flash。當Flash內容更新后,系統就可實現在加電時由CPLD配置控制器自動將配置文件下載到FPGA中。這樣在不需要任何硬體動作和專業軟體的情況下,只需要進行常規軟體操作就可以更新FPGA的配置文件。CPLD配置控制器主要是在配置FPGA時將FLASH存放的配置文件中的并行數據轉化為串列數據,實現系統的加電自運行。

3 嵌入式系統中FPGA 的配置電路設計

3.1 PS方式配置時序

在嵌入式系統中,配置控制器可以產生配置時序,能夠和FPGA直接通信,將FLASH 中的配置文件傳輸到FPGA 的SRAM 中去。通常使用PS被動串列方式進行配置FPGA,下面就通信中使用到的5根信號線的配置時序進行說明。

5根信號線分別為nCONFIG、nSTATUS、CONF_DONE、DCLK、DATA,連接配置控制器的5個I/O 口和對應的FPGA的引腳,配置時序圖如圖2所示。

圖2 PS方式配置信號時序圖

配置控制器上的5個I/O埠連接上述5個信號線。其中連接nCONFIG、DCLK、DATA埠設置成輸出態,nSTATUS、CONF_DONE埠設置成輸入態。當配置控制器開始與FPGA通信時,配置控制器首先在nCONFIG上送出一個大於8 um的負脈衝,並且檢測nSTATUS 上的信號。當FPGA 接收到nCONFIG上的下降沿時,迅速將nSTATUS和CONF_DONE拉低,並且保持低電平信號一直到nCONFIG抬高電平。當nCONFIG上抬高電平後過1 um,nSTATUS也將電平抬高,配置控制器檢測到nSTATUS上的變化后認為FPGA 已經做好了接收數據的準備。下一步配置控制器將產生配置時鐘脈衝,配置時鐘的第一個上升沿至少要比nSTATUS上升沿晚1 um。又由於配置數據和配置時鐘上升沿同步,所以在配置時鐘上升沿發生之前,數據線必須已經有了配置數據信號。配置數據是按照低位在前高位在後的順序把數據送上數據線。當所有數據都傳輸完畢后,CONF_DONE線上電平被抬高以示配置完畢。如果傳輸中出現了異常,FPGA迫使nSTATUS拉低電平,配置控制器一旦檢測到了這種現象將重新開始配置。由於配置文件中已經包含了FPGA初始化的一些代碼,所以傳輸完配置文件后,FPGA就可以正常工作了。

3.2 基於CPLD配置控制器的配置電路設計

CPLD是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是藉助Quartus II開發軟體平台,通過JTAG下載電纜將代碼傳送到目標晶元中,實現系統配置所需的時序要求和功能需求。而更重要的是CPLD配置控制器可以進行上萬次的燒寫操作。

嵌入式系統中FPGA 的PS方式配置方式電路設計如圖3所示。FPGA和FLASH、SSRAM組成了一個最基本的嵌入式系統,其中將Nios II軟核處理器嵌入到FPGA中。FLASH 作為程序的存儲器,其中存儲著系統的整個軟體應用程序和配置文件。SSAM作為系統程序運行空間,可以有效地解決配置控制器自身SRAM容量小的問題。

圖3 PS方式配置方式電路設計

在圖3所示的設計中,MSEL0和MSEL1是配置專用線,如果MSEL0接高電平(VCC),MSEL1接地(GND),則此時的配置模式為PS模式; 如果MSELO 和MSEL1都接地(GND),則配置模式為AS模式。CPLD控制器的控制信號MAX_control_signal主要包括flash_CS_n (片選)、flash_OE_n (輸出使能)、flash_RW_n (讀寫使能)、flash_RESET_n(重置)、flash_BYTE_n (位元組傳輸)等信號線。

配置文件通過Altera的Quartus II軟體以.pof(Programmer Object Files)文件格式下載到EPM7256配置控制器內,如果配置有錯誤,該配置控制器可以進行多次下載,直至最終完成配置功能。

FLASH中存儲的程序包括系統配置程序文件、軟體程序,其格式為.flash。系統加電后,配置控制器從FLASH 的0地址開始將配置文件進行並/串轉換后(即將圖3中的flash_DATA[7..0]轉換為DATA0)載入到FPGA中,完成系統加電時的自動配置功能;同時Nios II處理器將FLASH 中的應用程序移至到SSRAM 中運行,從而實現嵌入式系統的初運行。通過Nios II IDE工具可以將配置文件FPGA 的.sof文件格式轉換為Flash存儲器所需要的. flash文件格式。

4 配置文件的設計與實現

為了確保配置過程的正確,提高系統的配置性能,在配置文件設計時應嚴格按照FPGA的Ps配置流程進行,並在配置過程中始終監控配置工作狀態,在完善的配置程序配合下可以糾正如上電次序導致配置不正常等錯誤。該配置程序是採用VHDL語言編寫的,編寫完成後,將配置文通過JTAG介面下載到EPM7256配置控制器內,根據圖2的PS配置時序,其配置流程如下:

(1)配置信號的初始化:DATAO=0,DCLK=0,nCONFIG=0,CONF_DONE=1和nSTATUS=1,並保持2 us以上。

(2)檢測nSTATUS,如果為“0”,表明FPGA 已響應配置,可開始進行配置,否則報錯,並返回1。正常情況下,nCONFIG=0后1 us內nSTATUS為“0”。

(3)置nCONFIG=1,並延時5 us。

(4)DATAO上放置數據(低位在前),DCLK=1,延時。

(5)DCLK=0,並檢測nSTATUS,若為“0”,則報錯,重返1。

(6)準備下一位數據,並重新執行(4)、(5),直到數據發送完為止。

(7)此時CONF_DONE應變成“1”,表明FPGA已完成配置,如果數據發送完后,CONF_DONE為“0”,必須重新配置返回1。

(8)配置完成後,再送出299個周期(Cyclone要求的)的DCLK,以便FPGA完成初始化。

5 結束語

本文介紹了通過用CPLD 的MAX7000 系列配置控制器EPM7256和Flash實現Cyclone系列的EP1C6Q240C8 FPGA配置文件下載更新的方法。與傳統的JTAG或PROM 串列下載配置方法相比,此方法具有更新配置文件靈活方便、易於操作、更加有利於系統配置文件的升級等特點。與常用的串列配置方法相比,該配置方法更具有配置時間短,準確率高、易於實現等優點。雖然該配置控制電路是為配置Altera公司cyclone系列的FPGA器件而設計的,但稍加修改也適用於其它系列的。FPGA器件,故其有一定的通用性,採用此方法特別適用於需要不斷更新的系統設計中,具有較為廣闊的應用前景。

[admin via 研發互助社區 ] 用FPGA實現Nios II嵌入式系統配置技術已經有1935次圍觀

http://cocdig.com/docs/show-post-43056.html