1 狀態機的基本結構和功能

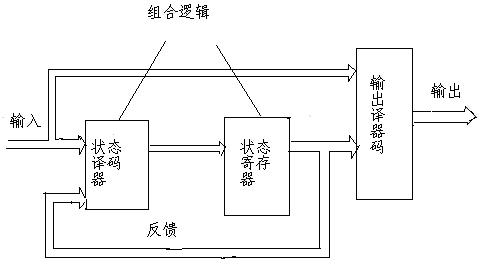

狀態機是一類很重要的時序電路,是許多數字電路的核心部件。狀態機的一般形式如圖1所示。除了輸入信號、輸出信號外,狀態機還包括一組寄存器,它用於記憶狀態機的內部狀態。狀態機寄存器的下一個狀態及輸出,不僅同輸入信號有關,而且還於寄存器當前狀態有關。寄存器可以認為是組合邏輯和寄存器邏輯的特殊組合。

圖1狀態機的結構示意圖

狀態機的基本操作有兩種:

(1) 狀態機內部狀態轉換。狀態機的下一狀態由狀態解碼器根據當前狀態和輸入條件決定。

(2) 產生輸出信號系列。輸出信號由輸出解碼器根據當前狀態和輸入條件決定。

狀態機的分類:

(1) 從狀態機的輸出方式分:Mealy型和Moore型。在摩爾狀態機中,其輸出只是當前狀態值的函數,並且僅在時鐘邊沿到來時才發生變化。

(2) 從結構上分:有單進程狀態機和多進程狀態機。

(3) 從狀態表達方式上分:有符號狀態機和確定狀態編碼的狀態機。

2用狀態機實現A/D採樣控制

對A/D器件進行採樣控制,傳統的方法多數是有CPU或單片機完成的。編程簡單,控制靈活,但缺點是控制周期長,速度慢。特別是當A/D本身的採樣速度比較快時,CPU的慢速極大地限制了A/D高速性能的利用。整個採樣周期需要4~6個狀態即可以完成。若FPGA的時鐘頻率為100MHz,從一 個狀態向另一狀態轉移的時間為一個時鐘周期,即10ns,那麼一個採樣周期為50ns,不到單片機60us採樣周期的千萬分之一。由此可見利用狀態機對A/D進行採樣控制是一種行之有效的方法。

2.1用狀態機對0809採樣控制

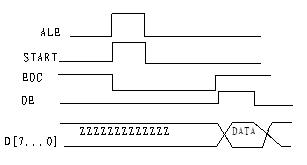

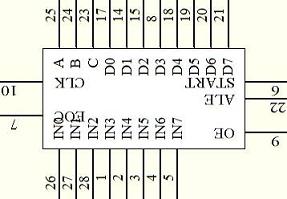

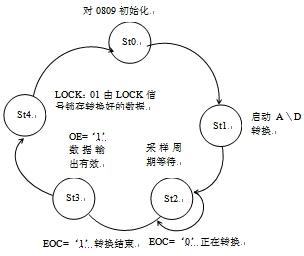

為了便於說明,以下以更為常見的、大家熟悉的ADC0809為例。圖2、3分別是0809的引腳圖、A/D轉換時序圖和採樣狀態控制圖,時序圖中,START為轉換控制信號,高電平有效;ALE為模擬信號輸入選通埠地址瑣序信號,上升沿有效;一旦START有效后,狀態信號EOC即變為低電平,表示進入轉化狀態,轉換時間大概100us。轉換結束后,EOC將變為高電平。此後外部控制可以使OE由低電平變為高電平(輸出有效),此時,0809的輸出數據匯流排D[0``7]從原來的高阻狀態變為輸出數據有效。由狀態圖可以看到,在狀態st2中需要對0809工作狀態信號EOC進行測試,如果為低電平,表示轉換沒有結束,仍需要停留在st2 狀態中等待,直到變成高電平后才說明轉換結束,在下一時鐘脈衝到來時轉向狀態st3。在狀態st3,由狀態機向0809發出轉換好的8位數據輸出命令,這一狀態周期同時可作為數據輸出穩定周期,以便能在下一狀態中向鎖存器中鎖入可靠的數據。在狀態st4,由狀態機向FPGA中的鎖存信號(LOCK的上升沿),將0809輸出的數據進行鎖存。

圖2 ADC0809工作時序和引腳圖

3 ADC0809採樣控制程序VHDL的設計

在對0809的工作時序了解后,再根據圖3寫出相應的VHDL代碼。以下程序含三個進程。REG進程是時序進程,它在時鐘信號CLK的驅動下,不斷將next_state中的內容賦給current_state,並由此信號將狀態變數傳輸給組合進程COM。組合進程COM有兩個主要的功能:

①狀態解碼功能,即從current_state信號中獲得的狀態變數,加上來自0809的狀態線信號EOC,決定下一個狀態的轉移方向,即確定次態的狀態變數;

②採樣控制功能,即根據current_state中的狀態變數確定對0809的控制信號線ALE、START、OE等輸出相應的控制信號,當採樣結束后還要通過LOCK向鎖存器件進程LATACH1發出鎖存信號,以便將0809的D[7..0]數據輸出口輸出的8位數據鎖存起來。

圖3控制ADC0809採樣狀態圖

3.1 VHDL的實現

在一完整的採樣周期中,狀態機中最先被啟動的是CLK為敏感信號的進程,接著是組合進程COM被啟動,因為它以信號current_state為敏感信號。最後被啟動的是瑣序器進程(LATCH1),將本採樣周期的輸出8位數據瑣序到寄序器中,以便外部電路從Q埠讀到穩定正確的數據。採用上三個進程,層次清晰,各進程分工明確。

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADCINT IS

PORT (D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK,EOC : IN STD_LOGIC;

ALE,START,OE,ADDA,LOCK0 : OUT STD_LOGIC;--ADDA,ADDB,ADDC用於選擇模擬信號輸入通道,但是--此處只有ADDA???

Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ADCINT;

ARCHITECTURE behav OF ADINT IS

TYPE states IS (st0,st1,st2,st3,st4);

SIGNAL current_state,next_state: states: =st0;

SIGNAL REGL :STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL LOCK :STD_LOGIC;

BEGIN

ADDA<='1';

Q<=REGL;; LOCK0<=LOCK;

COM: PROCESS(current_tate,EOC) BEGIN

CASE current_state IS

WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0';

next_state<=st1;

WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0';

next_state<=st2;

WHEN st2=>ALE<='0';START<='0';LOCK<='0';OE<='0';

IF (EOC='1')THEN next_state <=st3;--這是一個查詢EOC值的狀態

ELSE next_state<=st2;

END IF;

WHEN st3=>ALE<='0';START<='0';LOCK<='0';OE<='1';

next_state<=st4;

WHEN st4=>ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state<=st0;

WHEN OTHERS=>next_state<=st0;

END CASE;

END PROCESS COM;

REG: PROCESS (CLK) --這是最先啟動的process,因為這是clk敏感的。

BEGIN

IF(CLK'EVENT AND CLK'1')THEN current_state<=next_state;

END IF;

END PROCESS REG;

LATCH1: PROCESS (LOCK)

BEGIN

IF LOCK='1' AND LOCK'EVENT THEN REGL<=D;

END IF;

END PROCESS LATCH1;

END behav;

[admin via 研發互助社區 ] 利用有限狀態機控制A/D採樣已經有1976次圍觀

http://cocdig.com/docs/show-post-43041.html