以下我們將結合一個實例來簡要介紹一下如何在Nexar上實現一個完整的嵌入式系統設計過程。

首先:創建一個新的FPGA工程

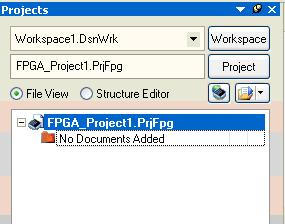

1、選擇菜單 [menus]File>>New>>FPGA Project,在工程欄中將會顯示新建的FPGA工程名,選擇菜單[menus]File>>Save Project,在對話框中修改工程名稱,然後Save。在工程欄中選擇File View選項,在工程中將會列出所有屬於當前工程的文件。註:Structure Editor選項用於編輯工程中文件間的鏈接關係。

圖1.1 工程欄----創建FPGA工程

2、FPGA工程可以支持原理圖和VHDL文件兩種源文件,採用混合編輯時,可以將VHDL生成圖表符的形式。選擇菜單[menus]File>>New>>Schematic;也可以在工程欄中選中FPGA工程名,然後點擊滑鼠,選擇[popups]Add New to Project>>Schematic。保存原理圖,重新命名為exercise.schdoc。

圖1.2 工程欄----創建原理圖

3、接下來在新加入的原理圖中完成一個最簡單的基於51內核的設計工程,實現LED閃亮的功能。在這個實例中,將會用到51的內核、RAM存儲器、上電時序控制、異或門、Nexus協議介面等FPGA工程器件。Nexar2004的器件均可以在FPGA集成庫中找到,在系統預設設置下,在窗口右側上方可以看到favorities/libraries/clipboard三個屬性欄,單擊libraries屬性欄,窗口中彈出集成庫窗口(見圖1.3)。選定設計中需要的器件,並拖拽到原理圖中。

| 器件名稱 | FPGA集成庫 |

| TSK51A_D | FPGA Processors.IntLib |

| RAMS_8x1K | FPGA Memories.IntLib |

| CLOCK_BOARD | FPGA NanoBoard Port-Plugin.IntLib |

| TEST_BUTTON | FPGA NanoBoard Port-Plugin.IntLib |

| LED | FPGA NanoBoard Port-Plugin.IntLib |

| NEXUS_JTAG_CONNECT | FPGA NanoBoard Port-Plugin.IntLib |

| NEXUS_JTAG_PORT | FPGA Generic.IntLib |

| OR2N1S | FPGA Generic.IntLib |

| FPGA_STARTUPx | FPGA Peripherals.IntLib |

圖1.3集成庫----51內核

圖1.4 設計實例-----原理圖

1、 按照系統設計的規則,將從集成庫中拖拽出了器件連接構建一個完整的數字電路系統。然後選擇[menu]Tools>>Annotate Quiet,系統將自動分配器件的標示,最後保存工程。特別應注意:

a.在Nexar2004中需要接入Nexus_JTAG_CONNECT和Nexus_JTAG_PORT這兩個器件用於構建Nexus協議鏈;

b.所有的輸入管腳均不能置空;否則編譯中系統會錯。

c. Bus Joiner  (圖示中用紅色標識的部分),可以將不同匯流排寬度的埠連接在一起。原則:輸出匯流排的寬度應不小於輸入匯流排寬度。

(圖示中用紅色標識的部分),可以將不同匯流排寬度的埠連接在一起。原則:輸出匯流排的寬度應不小於輸入匯流排寬度。

第二步,創建嵌入式軟體工程:

1、 選擇菜單 [menus]File>>New>>Embedded Project,在工程欄中將會顯示新建的Embedded工程名,選擇菜單[menus]File>>Save Project,在對話框中修改工程名稱,然後Save。

圖2.1嵌入式工程

2、 在工程欄中,用滑鼠點擊嵌入式工程名稱,然後選擇右鍵彈出[popus]Add New to Project>>C File。重新命名c文件名稱並保存;

3、 在c文件中輸入軟體代碼;

圖2.2設計實例---- c源代碼

第三步,設定嵌入式軟體工程選項:

1、選擇菜單[menu]Project>>Project Options,或者在工程欄,嵌入式工程名稱上單擊滑鼠右鍵選擇彈出菜單[popus]Project Options,系統將打開嵌入式工程的設置選項對話框(圖3.1),在configuration下拉選項欄中按照設計中選擇的微處理器的類型,選擇相應的嵌入式系統環境。由於前面我們設計的實例選用8051的微處理器核,因此在該工程的軟體設置重,如圖3.1選擇TASKING 8051。

圖 3.1嵌入式工程環境設置——微處理器設置

2、在Build Options下,點擊Processor並隨後點擊Startup Code。確認在Startup Code屬性欄下Generate and use startup code<project>_cstart.c選項欄被選中。由於在該文件中定義了嵌入式軟體工程的中斷向量表,這對選擇c編譯器而言非常重要。

3、點擊C Complier,選擇Memory Model並且在Select a complier memery model屬性欄中將下拉選擇Small:variables in DATA,然後確定Allow reentrant functions屬性未被選中。(圖3.2)

圖3.1嵌入式工程環境——C編譯環境設置

4、選擇Code Generation,選中Put strings in ROM only屬性並選中中斷向量屬性及寄存器屬性(圖3.3),然後完成對嵌入式軟體工程的環境設定。

圖3.3嵌入式工程環境——代碼發生器

第四步,設定微處理器的屬性選項:

如何將嵌入式工程與FPGA工程建立起相關聯的屬性呢? 接下來將講述具體的操作步驟;

1、 打開FPGA工程下的原理圖文件;

2、 滑鼠雙擊TSK51A_D Processor(U1),

3、在器件參數段中,在ChildCore1屬性欄中將在原理圖設計中與處理器核關聯的RAM的標識輸入,如圖4.1中用紅色標識的部分。在前面的設計實例中,外部RAM的標識為U4;

圖4.1器件屬性對話框

4、選擇菜單[menu]Project>>Complier FPGA Project Exercises_FPGA.PrjFpg,在編譯通過後保存;如圖4.2在工程欄中選擇Structure Editor屬性,在工程欄窗口下將顯示工程的結構層次關係,圖中將顯示出U1(TSK51A_D Processor)在設計中的位置關係;然後將嵌入式工程名稱拖拽到U1上(如圖4.2),從而在FPGA工程與嵌入式工程之間建立起相互關係;

圖4.2工程欄——結構編輯

4、 保存工程並選擇[menu]Project>>Re-complier FPGA Project。

第五步,FPGA的配置:

在工程設計完成後,要將編譯好的文件下載到系統板上驗證,假定選用的目標器件為Altera公司的Cyclone EP1C12Q240型號的FPGA,則需要在FPGA器件配置中添加相應的約束文件(Constraint File),前面介紹過,約束文件是用來指定選用FPGA器件的型號及定義引腳屬性的文件。FPGA配置的具體操作過程可以分以下幾步完成:

1、 選擇菜單[menu]Project>>Configuration Manager,或則在工程欄中,點擊FPGA工程名稱然後滑鼠右鍵,選擇彈出菜單[popus]Configuration Manager;

2、 在打開的配置管理器對話框中(圖5.1),在對話框的左下角設置區,點擊添加按鈕,在彈出的對話框中輸入配置文件名稱;

圖5.1FPGA工程配置管理器

3、 在約束文件區,點擊添加按鈕,在彈出的文件打開對話框中,選擇相應的約束文件名,點擊打開,然後將配置管理器中,配置選項選中;(見圖5.2)

圖5.2FPGA工程配置管理器——配置約束文件

4、在工程欄中,可以發現設置屬性下將新添一個約束文件,(如圖5.3)選擇菜單[menu]Project>>Recomplier FPGA Project,保存FPGA工程。

圖5.3工程欄——約束文件

最後,在系統控制面板上完成工程設計的全過程:

選擇菜單[menu]View>>Devices,或者點擊圖標 ,打開系統控制面板窗口(圖6.1);窗口中的三條黑線自上而下分別表示系統板間的物理鏈路、FPGA器件的硬體鏈路、綁定於Nexus協議上的IP器件軟鏈。在將系統開發板NanoBoard NB1上電前,應檢查系統開發板上並口匯流排是否已經與PC並口用扁平電纜連接完好。然後,選中窗口左上方的Live選項,窗口中將出現圖6.1中顯示的界面。在FPGA圖標的上方有四段工作流程,分別為編譯、綜合、裝配,下載。編譯用於檢查設計中的鏈接及軟體語法錯誤;綜合用於系統產生一個EDIF網表文件;裝配用於將EDIF文件翻譯成目標FPGA可以認識的對象文件,完成在FPGA中的布局布線,進行時序分析,最終生成用於下載到目標FPGA中的二進位代碼文件;下載用於完成將裝配好的二進位代碼文件下載到FPGA中的過程。當四個工作流程完成後,流程上的紅色狀態表識將變為綠色。如圖6.2

,打開系統控制面板窗口(圖6.1);窗口中的三條黑線自上而下分別表示系統板間的物理鏈路、FPGA器件的硬體鏈路、綁定於Nexus協議上的IP器件軟鏈。在將系統開發板NanoBoard NB1上電前,應檢查系統開發板上並口匯流排是否已經與PC並口用扁平電纜連接完好。然後,選中窗口左上方的Live選項,窗口中將出現圖6.1中顯示的界面。在FPGA圖標的上方有四段工作流程,分別為編譯、綜合、裝配,下載。編譯用於檢查設計中的鏈接及軟體語法錯誤;綜合用於系統產生一個EDIF網表文件;裝配用於將EDIF文件翻譯成目標FPGA可以認識的對象文件,完成在FPGA中的布局布線,進行時序分析,最終生成用於下載到目標FPGA中的二進位代碼文件;下載用於完成將裝配好的二進位代碼文件下載到FPGA中的過程。當四個工作流程完成後,流程上的紅色狀態表識將變為綠色。如圖6.2

圖6.1 系統控制——編譯前

圖6.2系統控制——編譯后

以上完成了從整個基於Altera Cyclone EP1C12型號FPGA項目工程的設計,通過將軟硬體設計方案在NanoBoard NB1系統開發板上實際運行驗證,再逐步優化,反覆下載驗證,最終完成項目的研發。

基本知識:

2、 Free-IP 核:(free- Intellectual Property Core,免版稅的器件內核)

在FPGA設計中越來越多的是一種基於IP的設計方法。所謂free-IP Core是指無需支付知識產權費用的、公開的器件設計文檔。

3、 虛擬儀器:(Virtual Instruments)

虛擬儀器是在PC技術的基礎上發展起來的,所以完全“繼承”了以現成即用的PC技術為主導的最新商業技術的優點,包括功能超卓的處理器和文件I/O,使您在數據導入磁碟的同時就能實時地進行複雜的分析。

4、 Nexus協議:(Nexus Protocol)

Nexus協議即IEEE-ISTO5001 – 1999 Global Embedded Processor Debug Interface 標準。Nexus協議是完全構架於IEEE1149.1(JTAG協議)之上,通過協議中定義的寄存器、通訊等標準,提供了通用的嵌入式處理器調試介面。

5、 Constraint File:

Constraint File是在FPGA設計中用於完成器件型號及管腳特性約束的描述性文件。所有的約束文件均保存在系統安裝目錄 \altium2004libraryFPGA中。

[admin via 研發互助社區 ] 在Nexar上實現一個完整的嵌入式系統已經有2108次圍觀

http://cocdig.com/docs/show-post-42984.html