在S3C2410 MMU(存儲器管理單元) 講解中我向大家介紹MMU的工作原理和對s3c2410 MMU部分操作進行了講解。我們知道MMU存在的原因是為了支持虛擬存儲技術,但不知道你發現了沒有,虛擬存儲技術的使用會降低整個系統的效率,因為與傳統的存儲技術相比,虛擬存儲技術對內存的訪問操作多了一步,就是對地址進行查表(查找映射關係),必須先從虛擬地址中分解出頁號和頁內偏移,根據頁號對描述符進行索引(這就是一個查表過程)得到物理空間的首地址,這樣做的代價是巨大的(其實這也正是時間效率與空間效率之間矛盾的一個體現),對某些嵌入式系統來說這簡直就是惡夢。那麼在引入了虛擬存儲技術之後有沒有方法在時間效率與空間效率這個矛盾之間取得一個平衡點呢?答案是有,我們可以通過一種技術從最大限度上降低這兩者的矛盾,這種技術是Caches(緩存)。也是我們本文要介紹的。

以下內容轉載自中計報

Cache的工作原理

Cache的工作原理是基於程序訪問的局部性。

對大量典型程序運行情況的分析結果表明,在一個較短的時間間隔內,由程序產生的地址往往集中在存儲器邏輯地址空間的很小範圍內。指令地址的分佈本來就是連續的,再加上循環程序段和子程序段要重複執行多次。因此,對這些地址的訪問就自然地具有時間上集中分佈的傾向。

數據分佈的這種集中傾向不如指令明顯,但對數組的存儲和訪問以及工作單元的選擇都可以使存儲器地址相對集中。這種對局部範圍的存儲器地址頻繁訪問,而對此範圍以外的地址則訪問甚少的現象,就稱為程序訪問的局部性。

根據程序的局部性原理,可以在主存和CPU通用寄存器之間設置一個高速的容量相對較小的存儲器,把正在執行的指令地址附近的一部分指令或數據從主存調入這個存儲器,供CPU在一段時間內使用。這對提高程序的運行速度有很大的作用。這個介於主存和CPU之間的高速小容量存儲器稱作高速緩衝存儲器(Cache)。

系統正是依據此原理,不斷地將與當前指令集相關聯的一個不太大的後繼指令集從內存讀到Cache,然後再與CPU高速傳送,從而達到速度匹配。

CPU對存儲器進行數據請求時,通常先訪問Cache。由於局部性原理不能保證所請求的數據百分之百地在Cache中,這裡便存在一個命中率。即CPU在任一時刻從Cache中可靠獲取數據的幾率。

命中率越高,正確獲取數據的可靠性就越大。一般來說,Cache的存儲容量比主存的容量小得多,但不能太小,太小會使命中率太低;也沒有必要過大,過大不僅會增加成本,而且當容量超過一定值后,命中率隨容量的增加將不會有明顯地增長。

只要Cache的空間與主存空間在一定範圍內保持適當比例的映射關係,Cache的命中率還是相當高的。

一般規定Cache與內存的空間比為4:1000,即128kB Cache可映射32MB內存;256kB Cache可映射64MB內存。在這種情況下,命中率都在90%以上。至於沒有命中的數據,CPU只好直接從內存獲取。獲取的同時,也把它拷進Cache,以備下次訪問。

Cache的基本結構

Cache通常由相聯存儲器實現。相聯存儲器的每一個存儲塊都具有額外的存儲信息,稱為標籤(Tag)。當訪問相聯存儲器時,將地址和每一個標籤同時進行比較,從而對標籤相同的存儲塊進行訪問。Cache的3種基本結構如下:

Cache與DRAM存取的一致性

在CPU與主存之間增加了Cache之後,便存在數據在CPU和Cache及主存之間如何存取的問題。讀寫各有2種方式。

……

你可以通過http://www.chinaunix.net/jh/45/180390.html閱讀完全文

s3c2410 內置了指令緩存(ICaches),數據緩存(DCaches),寫緩存(write buffer) , 物理地址標誌讀寫區 (Physical Address TAG RAM),CPU將通過它們來提高內存訪問效率。

我們先討論指令緩存(ICaches)。

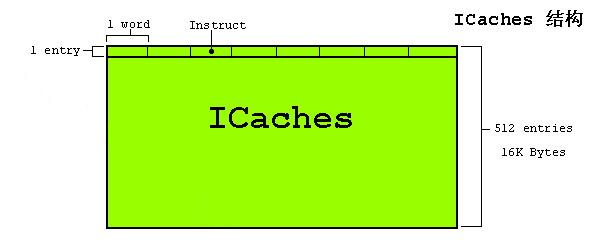

ICaches使用的是虛擬地址,它的大小是16KB,它被分成512行(entry),每行8個字(8 words,32Bits)。

當系統上電或重起(Reset)的時候,ICaches功能是被關閉的,我們必須往lcr bit置1去開啟它,lcr bit在CP15協處理器中控制寄存器1的第12位(關閉ICaches功能則是往該位置0)。ICaches功能一般是在MMU開啟之後被使用的(為了降低MMU查錶帶來的開銷),但有一點需要注意,並不是說MMU被開啟了ICaches才會被開啟,正如本段剛開始講的,ICaches的開啟與關閉是由lcr bit所決定的,無論MMU是否被開啟,只要lcr bit被置1了,ICaches就會發揮它的作用。

大家是否還記得discriptor(描述符)中有一個C bit我們稱之為Ctt,它是指明該描述符描述的內存區域內的內容(可以是指令也可以是數據)是否可以被Cache,若Ctt=1,則允許Cache,否則不允許被Cache。於是CPU讀取指令出現了下面這些情況:

通過以上的說明,我們可以了解到CPU是怎麼通過ICaches執行指令的。你可能會有這個疑問,ICaches總共只有512個條目(entry),當512個條目都被填充完之後,CPU要把新讀取近來的指令放到哪個條目上呢?答案是CPU會把新讀取近來的8個word從512個條目中選擇一個對其進行寫入,那CPU是怎麼選出一個條目來的呢?這就關係到ICaches的替換法則(replacemnet algorithm)了。ICaches的replacemnet algorithm有兩種,一種是Random模式另一種Round-Robin模式,我們可以通過CP15協處理器中寄存器1的RR bit對其進行指定(0 = Random replacement 1 = Round robin replacement),如果有需要你還可以進行指令鎖定(INSTRUCTION CACHE LOCKDOWN)。

關於替換法則和指令鎖定我就不做詳細的講解,感興趣的朋友可以找相關的資料進行了解。

接下來我們談數據緩存(DCaches)和 寫緩存(write buffer)

DCaches使用的是虛擬地址,它的大小是16KB,它被分成512行(entry),每行8個字(8 words,32Bits)。每行有兩個修改標誌位(dirty bits),第一個標誌位標識前4個字,第二個標誌位標識后4個字,同時每行中還有一個TAG 地址(標籤地址)和一個valid bit。

與ICaches一樣,系統上電或重起(Reset)的時候,DCaches功能是被關閉的,我們必須往Ccr bit置1去開啟它,Ccr bit在CP15協處理器中控制寄存器1的第2位(關閉DCaches功能則是往該位置0)。與ICaches不同,DCaches功能是必須在MMU開啟之後才能被使用的。

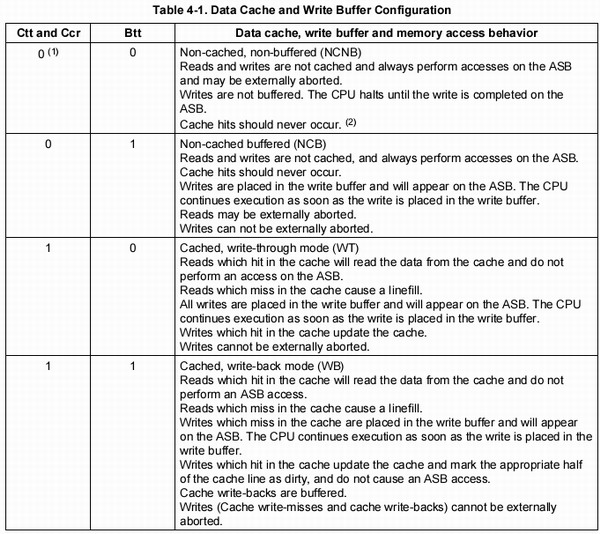

我們現在討論的都是DCaches,你可能會問那Write Buffer呢?他和DCaches區別是什麼呢? 其實DCaches和Write Buffer兩者間的操作有著非常緊密的聯繫,很抱歉,到目前為止我無法說出他們之間有什麼根本上的區別(-_-!!!),但我能告訴你什麼時候使用的是DCaches,什麼時候使用的是Write Buffer.系統可以通過Ccr bit對Dcaches的功能進行開啟與關閉的設定,但是在s3c2410中卻沒有確定的某個bit可以來開啟或關閉Write Buffer…你可能有點懵…我們還是來看一張表吧,這張表說明了DCaches,Write Buffer和CCr,Ctt (descriptor中的C bit),Btt(descriptor中的B bit)之間的關係,其中“Ctt and Ccr”一項裡面的值是 Ctt與Ccr進行邏輯與之後的值(Ctt&&Ccr).

從上面的表格中我們可以清楚的知道系統什麼時候使用的是DCaches,什麼時候使用的是Write Buffer,我們也可以看到DCaches的寫回方式是怎麼決定的(write-back or write-througth)。

在這裡我要對Ctt and Ccr=0進行說明,能夠使Ctt and Ccr=0的共有三種情況,分別是

Ctt =0, Ccr=0

Ctt =1, Ccr=0

Ctt =0, Ccr=1

我們分別對其進行說明。

到此為止我們用兩句話總結一下DCaches與Write Buffer的開啟和使用:

1.DCaches與Write Buffer的開啟由Ccr決定。

2.DCaches與Write Buffer的使用規則由Ctt和Btt決定。

DCaches與ICaches有一個最大的不同,ICaches存放的是指令,DCaches存放的是數據。程序在運行期間指令的內容是不會改變的,所以ICaches中指令所對應的內存空間中的內容不需要更新。但是數據是隨著程序的運行而改變的,所以DCaches中數據必須被及時的更新到內存(這也是為什麼ICaches沒有寫回操作而DCaches提供了寫回操作的原因)。提到寫回操作,就不得不提到PA TAG 地址(物理標籤地址)這個固件,它也是整個Caches模塊的重要組成部分。

簡單說PA TAG 地址(物理標籤地址)的功能是指明了寫回操作必須把DCaches中待寫回內容寫到物理內存的哪個位置。不知道你還記不記得,DCaches中每個entry中都有一個PA TAG 地址(物理標籤地址),當一個linefill發生時,被Cache的內容被寫進了DCaches,同時被Cache的物理地址則被寫入了PA TAG 地址(物理標籤地址)。除了TAG 地址(標籤地址),還有兩個稱為dirty bit(修改標誌位)的位出現在DCaches的每一個entry中,它們指明了當前entry中的數據是否已經發生了改變(發生改變簡稱為變“臟”,所以叫dirty bit,老外取名稱可真有意思 -_-!!!)。如果某個entry中的dirty bit置位了,說明該entry已經變髒,於是一個寫回操作將被執行,寫回操作的目的地址則是由PA TAG 地址(物理標籤地址)索引到的物理地址。

關於Caches,Write Buffer更詳細的內容請大家閱讀s3c2410的操作手冊:]

[admin via 研發互助社區 ] s3c2410 CACHES,WRITE BUFFER講解已經有2596次圍觀

http://cocdig.com/docs/show-post-42169.html