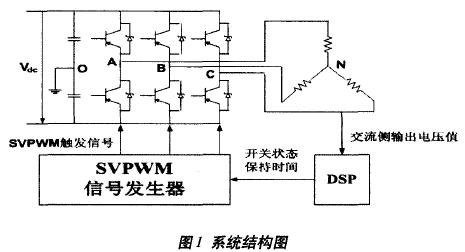

近年來,DSP在SVPWM(空間矢量脈寬調製)控制領域得到了廣泛應用。但是使用DSP單核心的控制方法仍然存在一些缺陷:基於軟體的:DSP在實現SVPWM觸發信號時需要較長的時鐘周期;微處理器中不確定的中斷響應會導致PWM脈衝的相位抖動。針對以上問題,本文提出了一種利用FPGA實現的SVPWM信號發生器,系統結構如圖1所示。作為DSP的外圍介面電路,該信號發生器能夠屏蔽DSP內部錯誤中斷對輸入時間信號的影響,保證輸出完整的SVPWM觸發信號波形,其三相併行處理結構還能夠有效提升系統的動態響應速度。

SVPWM簡介

SVPWM的主要思想在於利用逆變器空間電壓矢量的切換合成參考電壓矢量。具體方法如下:在橋式電路中,同一橋臂上兩個開關的工作狀態在任意時刻都是互補的,所以可以用二值邏輯函數表示6個 開關的工作狀態:

由式1可見,3組開關的工作狀態共有23=8種,不同的開關工作狀態對應著不同的三相輸出電壓。這8種工作狀態分別對應著8條基本空間電壓矢量,任意區域內的空間電壓參考矢量都可以由2條非零矢量以及2條零矢量合成。在進行電壓矢量合成時,規定每一次開關動作只能有一相橋臂的工作狀態發生轉換,目的是為了降低電路中的諧波含量,確定基本電壓矢量的切換順序。

SVPWM信號發生器的設計

基本原理

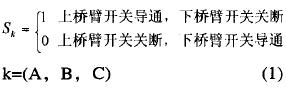

圖1中DSP採集逆變器交流側輸出電壓值,並通過計算得到橋式電路開關的狀態保持時間。SVPWM信號發生器將DSP的輸入時間信號轉換為開關觸發信號,在結構上可以分為數據鎖存器和有限狀態機兩個模塊,其頂層文件原理圖如圖2所示。

在狀態機的一個工作周期內,輸入時間信號的突變會使狀態機的工作狀態發生不規則跳變,對輸出信號造成巨大影響,無法得到所需要的SVPWM 觸發信號。因此,圖2中LATCH鎖存器模塊的作用就是鎖存輸入時間數據TIME1_A、TIME0_A、TIME1_B、TIME0_B、TIME1_C 、TIME0_C,直至狀態機的當前工作周期結束(即"ORDER"命令有效),從而避免外界對狀態機工作狀態的影響,保證狀態機按照輸入時間數據要求完成工作狀態的轉換。

利用有限狀態機的方法設計FPGA,只須控制三相橋臂開關狀態的保持時間,就可以實現SVPWM 觸發信號。圖2中FSMS主要由1個基準計數器和3個比較器構成,輸入時間數據預存在3個比較器內,通過比較基準計數器當前值和比較器中的預存數據控制FSMS工作狀態的轉換, 同時根據不同的比較結果生成不同的三相橋臂開關驅動信號。如果基準計數器當前值等於預存輸入時間,說明狀態機當前工作狀態已經完成,要轉入下一個工作狀態,相應的觸發信號也要改變;如果基準計數器當前值不等於預存輸入時間,說明狀態機當前工作狀態尚未完成,需要繼續保持當前工作狀態,相應的觸發信號也保持不變。狀態機按照輸入時間信號的要求轉換自身工作狀態,使觸發信號產生相應變化,從而實現時間信號向SVPWM 觸發信號的轉變。另外,由於FSMS內部比較器參照同一基準計數器,因此三相觸發信號之間不存在時間延遲,得到的是并行的三相觸發信號。

設計方法

本設計採用自頂向下、層次化、模塊化的設計思想。

LATCH鎖存器模塊由6個并行的6位數據鎖存器構成,所有鎖存器均使用圖2中的"ORDER"作為數據鎖存信號,具體規定如下:

1)"ORDER" 信號作為鎖存器工作進程的唯一敏感信號參量,只有其信號值發生變化時才會啟動鎖存器的工作進程,否則鎖存器不做出任何響應;

2)當"ORDER"信號發生變化,且當前值為1時,鎖存器中的存儲數據得以釋放,被輸入FSMS,新的時間數據同時輸入鎖存器;

3)當"ORDER"信號發生變化,且當前值為0時,鎖存器鎖存已輸入時間數據,保持FSMS的時間輸入數據不變, 同時拒絕新數據輸入;

4)鎖存器的數據鎖存時間等於FSMS中基準計數器的一個工作周期。當基準計數器完成一個工作周期時,"ORDER"信號將被置'1',其餘時間,"ORDER"信號被置'0'。

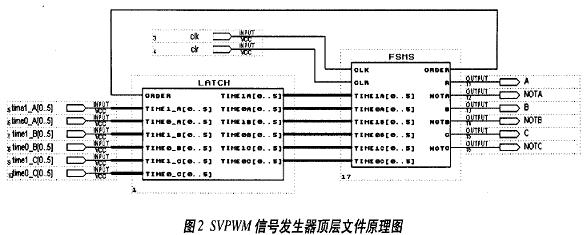

為了得到三相併行輸出的SVPWM觸發信號.FSMS模塊內部設計了3個狀態機分別控制A、B、C相輸出。根據式1,假設上橋臂每個開關在一個周期內工作狀態的轉換順序都是"1-0-1",因此可以將每個狀態機都設計為3種狀態.分別代表每一相開關在一個周期內的3個工作狀態,工作狀態的保持時間由輸入時間決定。當輸入時間信號發生變化時,FSMS 工作進程啟動。具體流程如圖3所示。

以A相橋臂為例(另外兩相橋臂的控制方法與A相橋臂類似),狀態機進程啟動后,基準計數器開始計時,比較器實時比較計數器當前值和比較器內部預存的時間。計數器的一個工作周期可以分為三個階段:

1)計數器當前值小於輸入時間TIME1_A時.狀態機處於"00"態.A相上橋臂輸出為'1';

2)計數器當前值大於等於輸入時間TIME1_A而小於TIME1_A與TIME0_A的和時,狀態機處於"01"態,A相上橋臂輸出為'0';

3)計數器當前值大於等於TIME1_A與TIME0_A的和時,狀態機處於"10"態,A相上橋臂輸出為'1'。

如果狀態機處於非法狀態"11",則圖2中管腳A和NOTA輸出為高阻態。

模擬結果

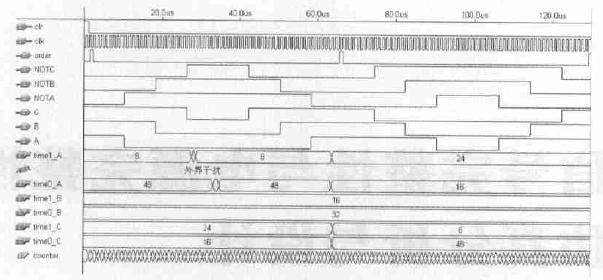

利用MAX+PLUS II軟體對本設計的邏輯功能進行模擬驗證,模擬時間為0~120us,時鐘頻率為1MHz。

採用EPM3256ATC144-7FPGA晶元進行邏輯編程后,共佔用166個邏輯單元,晶元利用率為64%,具有較大的擴展空間。模擬結果如圖4所示。

圖4中輸出信號A和NOTA,B和和NOTB,C和NOTC分別代表橋式電路3組互補開關的驅動命令,輸入信號time1_A、time1_B、time1_C和time0_A,time0_B、time0_C分別代表各開關高低電平狀態的保持時間。通過模擬波形可以看到,FPGA實現了空間矢量的轉換,開關的狀態保持時間取決於輸入信號time0_A、time0_B、time0_C和time1_A、time1_B、time1_C,完全實現了時間信號到觸發信號的轉換。而且,A相橋臂有效地抵抗了外界干擾,沒有受到輸入時間信號突變的影響,表明SVPWM信號發生器具有良好的抗干擾能力。

結語

本文用VHDL硬體描述語言設計了一種由鎖存器陣列和有限狀態機構成的SVPWM信號發生器,該信號發生器不僅成功實現了輸入時間信號到SVPWM觸發信號的轉換,而且具有良好的抗干擾能力。此外,其并行處理結構可以保證三相橋臂開關同時動作,有效地提升了控制系統的整體性能。由於SVPWM信號發生器是用VHDL硬體描述語言實現的IP核.因而可簡便地應用於逆變器控制系統中。

[admin via 研發互助社區 ] SVPWM信號發生器的VHDL實現已經有3486次圍觀

http://cocdig.com/docs/show-post-43072.html