概述

運放電源去耦旁路措施每個集成運放的電源引線,一般都應採用去耦旁路措施,即從電源引線端到地跨接一個高性能的電容,如圖所示。圖中的高頻旁路電容,通常可選用高頻性能優良的陶瓷電容,其值約為0.1μF。……

| 運放電源去耦旁路措施

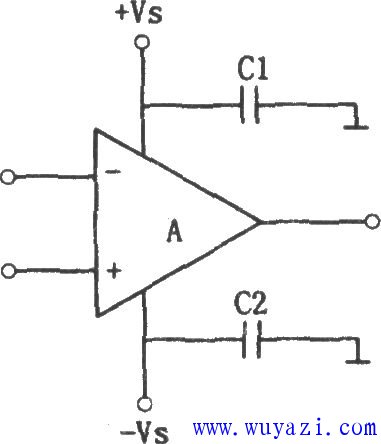

每個集成運放的電源引線,一般都應採用去耦旁路措施,即從電源引線端到地跨接一個高性能的電容,如圖所示。圖中的高頻旁路電容,通常可選用高頻性能優良的陶瓷電容,其值約為0.1μF。或採用lμF的鉭電容。這些電容的內電感值都較小。在運放的高速應用時,旁路電容C1和C2應接到集成運放的電源引腳上,引線盡量短,這樣可以形成低電感接地迴路。當所使用的放大器的增益帶寬乘積大於10MHz時,應採用更嚴格的高頻旁路措施,此時應選用射頻旁路電容,如0.1μF圓片陶瓷電在,同時每個印刷板或每4~5個集成晶元再增加一對(C1和C2)鉭電容。對於通用集成晶元,對旁路的要求不高,但也不能忽視,通常最好每4~5個器件加一套旁路電容。不論所用集成電路器件有多少,每個印刷板都要至少加一套旁路電容。 |

[admin

via

研發互助社區 ]

運放電源去耦旁路措施已經有1656次圍觀

http://cocdig.com/docs/show-post-25296.html