摘要:簡要敘述了常用的信號處理系統的類型與處理機結構,介紹了正逐步得到廣泛應用的DSP+FPGA處理機結構,在此基礎上提出了一種實時信號處理的線性流水陣列,並舉例說明了該結構的具體實現,最後分析說明了此結構的優越性。

實時信號處理系統要求必須具有處理大數據量的能力,以保證系統的實時性;其次對系統的體積、功耗、穩定性等也有較嚴格的要求。實時信號處理演算法中經常用到對圖象的求和、求差運算,二維梯度運算,圖象分割及區域特徵提取等不同層次、不同種類的處理。其中有的運算本身結構比較簡單,但是數據量大,計算速度要求高;有些處理對速度並沒有特殊的要求,但計算方式和控制結構比較複雜,難以用純硬體實現。因此,實時信號處理系統是對運算速度要求高、運算種類多的綜合性信息處理系統。

1 信號處理系統的類型與常用處理機結構

根據信號處理系統在構成、處理能力以及計算問題到硬體結構映射方法的不同,將現代信號處理系統分為三大類:

從系統信號處理系統的構成方式來看,常用的處理機結構有下面幾種:單指令流單數據流(SISD)、單指令流多數據流(SIMD)、多指令流多數據流(MIMD)。

2 DSP+FPGA結構

隨著大規模可編程器件的發展,採用DSP+ASIC結構的信號處理系統顯示出了其優越性,正逐步得到重視。與通用集成電路相比,ASIC晶元具有體積小、重量輕、功耗低、可靠性高等幾個方面的優勢,而且在大批量應用時,可降低成本。

現場可編程門陣列(FPGA)是在專用ASIC的基礎上發展出來的,它克服了專用ASIC不夠靈活的缺點。與其他中小規模集成電路相比,其優點主要在於它有很強的靈活性,即其內部的具體邏輯功能可以根據需要配置,對電路的修改和維護很方便。目前,FPGA的容量已經跨過了百萬門級,使得FPGA成為解決系統級設計的重要選擇方案之一。

DSP+FPGA結構最大的特點是結構靈活,有較強的通用性,適於模塊化設計,從而能夠提高演算法效率;同時其開發周期較短,系統易於維護和擴展,適合於實時信號處理。

實時信號處理系統中,低層的信號預處理演算法處理的數據量大,對處理速度的要求高,但運算結構相對比較簡單,適於用FPGA進行硬體實現,這樣能同時兼顧速度及靈活性。高層處理演算法的特點是所處理的數據量較低層演算法少,但演算法的控制結構複雜,適於用運算速度高、定址方式靈活、通信機制強大的DSP晶元來實現。

3 線性流水陣列結構

在我們的工作中,設計並實現了一種實時信號處理結構。它採用模塊化設計和線性流水陣列結構(圖1)。

這種線性流水陣列結構具有如下特點:

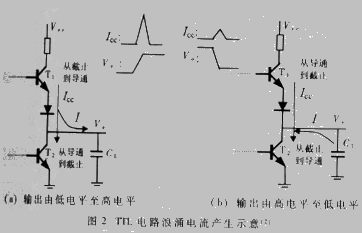

每個PU的核心由DSP晶元和可重構器件FPGA組成,另外還包括一些外圍的輔助電路,如存儲器、先進先出(FIFO)器件及FLASHROM等(圖2)。可重構器件電路與DSP處理器相連,利用DSP處理器強大的I/O功能實現單元電路內部和各個單元之間的通信。從DSP的角度來看,可重構器件FPGA相當於它的宏功能協處理器(Co-processor)。

PU中的其他電路輔助核心電路進行工作。DSP和FPGA各自帶有RAM,用於存放處理過程所需要的數據及中間結果。FLASHROM中存儲了DSP的執行程序和FPGA的配置數據。先進先出(FIFO)器件則用於實現信號處理中常用到的一些操作,如延時線、順序存儲等。每個PU單獨做成一塊PCB,各級PU之間通過插座與底板相連。底板的結構很簡單,主要由幾個串連的插座構成,其作用是向各個PU提供通信通道和電源供應。可以根據需要安排底板上插座的個數,組成多級線性陣列結構。這種模塊化設計的突出優點在於,它使得對系統的功能擴充和維護變得非常簡單。需要時,只要插上或更換PU電路板,就可以實現系統的擴展和故障的排除。每一級PU中的DSP都有通信埠與前級和后級PU電路板相連,可以很方便地控制和協調它們之間的工作。

4 應用實例

我們應用上述線性流水陣列結構實現了一個實時目標檢測系統,該系統的任務主要是接收攝像頭輸出的灰度圖象,經預處理、編碼、直線擬合和目標識別後,輸出結果到PC機顯示。在這個任務中,預處理模塊包括抽樣、卷積和編碼等步驟,屬於低層的處理,其運算數據量大,但運算結構較規則,適於用FPGA進行純硬體實現;而直線擬合及目標識別等高層圖象處理演算法,所處理的數據量相對較少,但要用到多種數據結構,其控制也複雜得多,我們用DSP編程來實現。

重構處理模塊採用的是Xilinx公司的XC5200系列FPGA晶元。這是一種基於SRAM的現場可編程門陣列。表1給出了XC5200 系列FPGA的一些參數。

表1 XC5200系列FPGA的一些參數

| 器件 | XC5204 | XC5206 | XC5210 | XC5215 |

| 邏輯單元 | 480 | 784 | 1296 | 1936 |

| 最大邏輯門 | 6000 | 10000 | 16000 | 23000 |

| 多功能塊 | 10×12 | 14×14 | 18×18 | 22×22 |

| CLB | 120 | 196 | 324 | 484 |

| 觸發器 | 480 | 784 | 1296 | 1936 |

| I/O | 124 | 148 | 196 | 244 |

XC5200系列FPGA邏輯功能的實現由內部規則排列的邏輯單元陣列(LCA)來完成,它是FPGA的主要部分。LCA的核心是可重構邏輯塊(CLB),四周是一些輸入/輸出塊(IOB)。CLB和IOB之間通過片內的布線資源相連接。LCA由配置代碼驅動,CLB和IOB的具體邏輯功能及它們的互聯關係由配置數據決定。整個FPGA模塊的設計實現在Xilinx公司的Foundation 2.1i開發平台上完成。該系統支持設計輸入、邏輯模擬、設計實現(設計綜合)和時序模擬等系統開發全過程。

在選用DSP晶元時,主要應考慮性能能否滿足快速判讀演算法的要求,具體說就是要求選擇那些指令周期短、數據吞吐率高、通信能力強、指令集功能完備的處理器,同時也要兼顧功耗和開發支持環境等因素。表2列出了一些常用微處理器的性能參數。

我們選擇的是應用廣泛、性價比較高的TMS320C40晶元。它是美國TI公司推出的為滿足并行處理需求的32位浮點DSP。主要特性如下:

表2 常用微處理器對照表

| 處理器類型 | DSP(Motorola) | ADSP | TMS320 | ||||

| 96002 | 56156 | 21020 | 2101 | C30 | C40 | C50 | |

| 字長/bit | 32 | 16 | 32 | 16 | 32 | 32 | 16 |

| 指令周期/ns | 50 | 50 | 50 | 60 | 33 | 25 | 50 |

| 1024浮點FFT時間/ms | 1.04 | 2.33 | 0.96 | 2.07 | 2.36 | 1.93 | 3.42 |

從結構和功能上看,C40很適合與可重構器件互相配合起來構成高速、高精度的實時信息處理系統,並完全可以勝任圖像信息的實時處理任務;此外,C40的開發系統也比較完備,支持C語言和彙編語言編程,能夠方便地進行演算法移植和軟/硬體的協同設計。

衡量系統的整體性能不僅要看所使用的器件和所能完成的功能,還要看器件之間採用怎樣的互連結構。XC5200可以完成模塊級的任務,起到DSP的協處理器的作用。它的可編程性使它既具有專用集成電路的速度,又具有很高的靈活性。C40內部結構的主要優勢是:所有指令的執行時間都是單周期,指令採用流水線,內部的數據、地址、指令及DMA匯流排分開,有較多的寄存器。這些特徵使它有較高的處理速度。FPGA具有硬體的高速性,而C40具有軟體的靈活性,從器件上考察,能夠滿足處理複雜演算法的要求。同時,C40的6個通信口和6個DMA通道使其能夠在不被中斷的情況下比較從容地應付與外界大量的數據交換。

從PU內部互連來看,C40使用了專用的通信口完成與FPGA的互連,能夠保證在任何情況下FPGA與C40的數據通道的暢通。另外,FPGA和C40各自都有輸入埠,使得系統的處理結構多樣化。比如,FPGA可以作為處理流程中的一個模塊,獨立完成某項功能,也可以作為C40的協處理器,通過C40的調用來完成特定的子函數。底板將互連性延伸到PU之間,使得多個電路板能夠組成多處理機系統。前級的C40既可以與下一級的C40通信,也可以將數據發送到下一級的FPGA。

綜上所述,本文提出的基於DSP+FPGA的線性流水陣列結構,為設計中如何處理軟硬體的關係提供了一個較好的解決方案。同時,該系統具有靈活的處理結構,對不同結構的演算法都有較強的適應能力,尤其適合實時信號處理任務。

[admin via 研發互助社區 ] DSP+FPGA 實時信號處理系統已經有1854次圍觀

http://cocdig.com/docs/show-post-45152.html