一個映像平面(image plane)是一層銅質導體(或其它導體),它位於一個印刷電路板(PCB)裡面。它可能是一個電壓平面,或鄰近一個電路或訊號路由層(signal routing layer)的0V參考平面。1990年代,映像平面的觀念被普遍使用,現在它是工業標準的專有名詞。本文將說明映像平面的定義、原理和設計。

映像平面的定義

射頻電流必須經由一個先前定義好的路徑或其它路徑,回到電流源;簡言之,這個回傳路徑(return path)就是一種映像平面。映像平面可能是原先的走線的鏡像(mirror image),或位於附近的另一個路徑----亦即,串音(crosstalk);映像平面也許就是電源平面、接地平面,或者自由空間(free space)。射頻電流會以電容或電感的形式與任何傳輸線耦合,只要此傳輸線的阻抗比先前定義好的路徑的阻抗小。不過,為了符合EMC標準,必須避免讓自由空間成為回傳路徑。

雖然單面PCB可以降低成本,但是這種簡單的結構可能無法符合EMC標準。大多數的2層或4層結構的PCB具有比較高的訊號完整性,並且可以通過 EMC測試。高密度(多層板)的PCB堆棧大約可以為每一對映像平面,提供6dB至8dB的射頻抑制,這是由於消除磁通量所產生的效果。有一個簡單法則可以用來判斷何時應該使用多層板:當頻率速率超過5MHz,或上升時間比5 ns快,就必須使用多層板。

電感的定義

走線和銅質平面都具有數目有限的電感,當電壓施加到走線或傳輸線時,這些電感會禁止電流產生,所以會使雙導線成為不平衡的共模輻射,磁通量因此無法降低。在電路板結構中,具有三種不同的電感型態:

和電容、電阻相比,電感值是最難被測量的。電感代表一個封閉型電流迴路的動態特性。電感是通過封閉迴路的磁通量和產生磁通量的電流之比值,其數學表述式是:Lij=Ψij / li ,Ψ是磁通量,I是迴路中的電流。在一個封閉迴路中,電感值與迴路形狀和大小有關。當設計PCB時,工程師經常會忽視走線的電感大小。電感永遠和封閉迴路有關。封閉迴路的電感效應,可以由部份電感和共同的部份電感的效應來描述。

部份電感

一個導體的內部電感,它是由此導體內部的磁通量產生的。一個封閉迴路的部份電感之加總,等於將每個區段的部份電感相加后的和,亦即。而每一個區段的Li就等於Ψi / li, Ψi表示第i個區段耦合至迴路的磁通量,I是在第i個區段的電流量,Li就是部份電感。因此,不同迴路將會有不同數值的部份電感。我們關注的是部份電感值,而不是走線的總電感值。而且,利用部份電感可以推導出共同的部份電感。

共同的部份電感

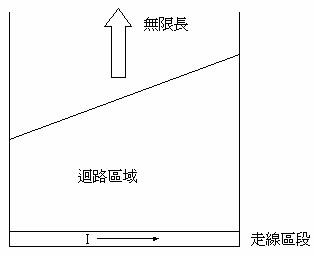

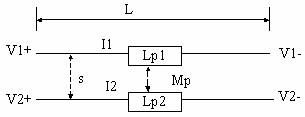

可以讓映像平面消除磁通量的主要因素是來自於「共同的部份電感」。磁通量被消除之後,能夠讓磁力線連結,並為射頻電流找到最佳的回傳路徑。自身的部份電感是指特定的迴路區段之電感,和其它迴路區段無關。附圖一是表示一個自身的部份電感,一條走線迴路內的電流是I,Lp是走線區段的自身的部份電感。假設此走線是從有限的一端,一直延伸至無限的另一端。

圖一:自身的部份電感

理論上,雖然自身的部份電感與鄰近的導線無關,但實際上,間距很小的相鄰導線會互相改變彼此的自身的部份電感值。這是因為一條導線會和其它導線互動,使得在導線的全部長度上的電流分佈不再一致化(uniform)。尤其當兩導線間隔和半徑的比值約小於5:1時,這種情況會更加明顯。

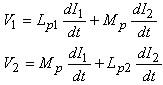

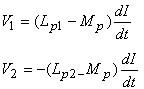

在兩條導線之間,會有共同的部份電感存在。共同的部份電感Mp是以平行走線,或導線區段之間的間距(s)為基礎。Mp是「第一條導線內的電流所產生的磁通量(通過第二條導線至很遠的地方)」和「第一條導線所產生的電流」之比值。附圖二是表示一個共同的部份電感。它的等效電路如附圖三所示,此電路的數學表述式如下所示:

圖二:共同的部份電感

現在以共同的部份電感之觀念,來考慮在附圖三的電路上傳送訊號,譬如:頻率訊號。V1是在訊號路徑上,V2是在射頻電流回傳路徑上。假設此兩導線構成一個訊號路徑和它的回傳路徑,因此I1= I且I2 = -I。要不是有共同的部份電感存在,此兩導線將無法互相耦合,此電路也無法正常工作,也不會形成一個封閉迴路。在附圖三中的電壓降將變成:

圖三:兩導線之間的共同的部份電感

由上式中可以知道,若要使電壓降變小,必須增加共同的部份電感值(Mp)。

而增加共同的部份電感之最簡單方法是:將射頻回傳電流的路徑盡量和訊號走線靠近。最佳的設計方法是:在接近訊號走線的附近,使用一個射頻回傳平面,它們之間的距離在可實現的能力範圍之內,應該盡量的小。

部份電感永遠存在於導線中,它如同默認值一樣。因此,它就等同於一個具有特定的諧振頻率的天線。「共同的部份電感」可以降低「部份電感」的效應。縮小兩導線的間距,其個別的部份電感就可以降低,這可以符合EMI兼容標準的要求。

為了使共同的部份電感之效應達到最大,在兩導線中的電流必須大小相同,但方向相反。這也是為何映像平面(或接地線)能夠如此有效的原因。在兩條平行的導線之間,有共同的部份電感存在,而這些電感值會隨著兩導線的間距和長度之不同而變化(可以參考導線的技術規格)。當兩平行導線的間距和長度都最小時,它們的共同的部份電感值會最大。

若在電源和接地平面之間以介電材料分開,此時「共同的部份電感」將扮演什麼角色呢?同樣的,只要這兩個平面的間距很小,共同的部份電感值就會很大。此時,在電源平面上所測量到的射頻訊號電流應該為零,因為它被大小相同、方向相反的射頻回傳電流抵銷了。

此外,須注意的是,如果降低兩導線之間的共同的部份電感值,不僅會減損映像平面的效應,而且會使兩平面之間的電容值增加。

映像平面的設計

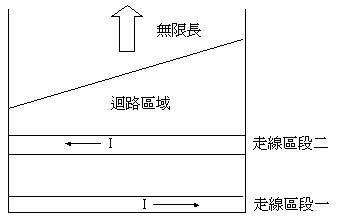

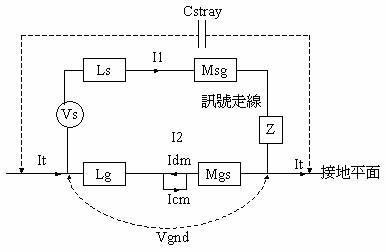

附圖四是在PCB內的映像平面,它具有共同的部份電感。在此圖中,訊號走線的大多數射頻電流將回至接地平面,此平面在訊號走線的正下方。在這個回傳「映像」結構中,射頻回傳電流將遇到一個有限大的阻抗(電感)。此回傳電流會產生一個「電壓梯度(斜率)」(每單位路徑長度的電壓變化率),也稱為「接地雜訊電壓(ground-noise voltage)」。接地雜訊電壓會導致部份的訊號電流通過接地平面的離散電容。

圖四:PCB內的接地平面

典型的共模電流是差模電流Idm的1/10n倍(n為小於10的正整數)。不過,共模電流(I1和Icm)會比差模電流( 和 )產生更多的輻射。這是因為共模的射頻電流場是相加的,而差模電流場是相減的。

為了降低「接地雜訊電壓」,必須增加走線和其最靠近的映像平面之間的共同的部份電感值。這樣可以為回傳電流提供一條增強的路徑,將映像電流映射回電流源。接地雜訊電壓Vgnd的計算公式如下所示:

Vgnd = Lg dI2/dt - Mgs dI1/dt

附圖四和上式的符號意義如下所示:

Ls = 訊號走線自身的部份電感。

Msg = 訊號走線和接地平面之間的共同的部份電感。

Lg = 接地平面自身的部份電感。

Mgs = 接地平面和訊號走線之間的共同的部份電感。

Cstray = 接地平面的離散(stray)電容。

Vgnd = 接地平面雜訊電壓。

為了降低附圖四中的If,接地雜訊電壓必須減少。最好的方法是:縮小訊號走線和接地平面之間的距離。在大多數的情況下,接地雜訊的降低是有極限的,因為訊號平面和映像平面之間的距離不能小於一個特定值;若低於此值,則電路板的固定阻抗和功能將無法確保。此外,也可以為射頻電流提供額外的路徑,藉此降低接地雜訊電壓。此額外的回傳路徑包含有數條接地線。

一個穩固的平面會產生共模的輻射。由於共同的部份電感可以降低具輻射性的射頻電流的產生,因此,共同的部份電感也會影響到差模電流和共模電流。而利用映像平面是可以將這些電流大幅地降低的。理論上,差模電流應該等於零,但實際上它無法100%被消除,而剩下來的差模電流會轉變成共模電流。此共模電流正是造成電磁干擾的主要來源。因為在回傳路徑上的剩餘的射頻電流,被加到在訊號路徑中的主電流(I1)中,造成訊號嚴重干擾。為了降低共模電流,我們必須將走線平面和映像平面之間的共同的部份電感值增加至最大,以補捉磁通量,藉此消除不需要的射頻能量。差模電壓和電流會產生共模電流,而減少差模電流的方法除了增加共同的部份電感值以外,走線平面和映像平面之間的距離也必須最小。

在PCB內,當有一個射頻回傳平面或路徑存在時,若此回傳路徑被連接至一個參考源,則可以獲得最佳的性能。對TTL和CMOS而言,其晶元內的功率和接地腳位是連接至參考源、電源、接地平面。只有當射頻回傳路徑有和晶元內的功率和接地腳位連接,一個真正的映像平面才會存在。通常,在晶元內會有接地線路,此線路與PCB的接地平面連接,因此產生良好的映像平面。如果將此映像平面移除,則在走線和接地平面之間會產生「虛幻的」映像平面。由於走線之間的距離很小,輻射能量會降低,因此,射頻映像(RF image)會被抵銷。理想的映像平面應該是無限大的,而且沒有分裂、細縫或割痕。

接地和訊號迴路

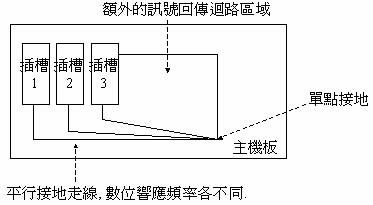

由於迴路是射頻能量傳播最主要的媒介,因此,接地或訊號回傳迴路控制(return loop control)是抑制PCB內的電磁干擾的最重要設計考慮之一。高速的邏輯組件和振蕩器應該盡量靠近接地電路,以避免形成迴路;在此迴路中會有渦流(eddy current)存在,此時是以機殼或底座(chassis)接地。渦流是受到不斷變化的磁場感應產生的,它通常是寄生的。附圖五是PC的適配卡插槽和單點接地所形成的迴路。在此圖中,有一個額外的訊號回傳迴路區域存在。每個迴路將會各別產生一個不同的電磁場和頻譜。射頻電流將會在特定的頻率下,產生電磁輻射場,其輻射能量的大小和迴路的面積有關。這時必須使用遮蔽物(containment),以避免射頻電流耦合至其它電路中;或輻射至外部環境,造成電磁干擾。不過,最好能盡量避免由內部電路產生射頻迴路電流(RF loop current)來。

圖五:在PCB內的接地迴路

若射頻電流的回傳路徑不存在,此時,可以利用連接至底座的接地線路,或0V參考源來協助移除掉不良的射頻電流。這也稱為「迴路面積控制(loop area control)」。

迴路面積的控制

一個被磁場感應的迴路,它的電磁場可以用電壓源來表示。這個電壓源大小和迴路的總面積成正比。因此,為了降低磁場的耦合效應,必須減少迴路的面積。電場「撿拾(pickup)」接收系統也是依靠迴路面積,來形成接收天線。

當有一個電場存在時,在電源和接地平面之間,會產生一個電流源。電場不會在線路至線路之間耦合,而會在走線至接地線之間耦合,這就包含了共模電流。但是,對磁場而言,由於電場會伴隨它產生,所以電磁場會在線路至線路之間耦合,也會在走線至接地線之間耦合。

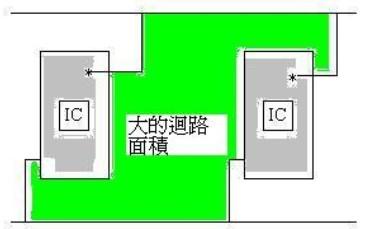

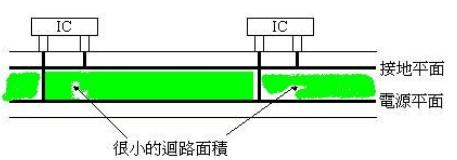

一般人都會忽略在PCB內,於電源和0V參考點之間要設置迴路區域。附圖六的大迴路面積是最容易設計的,但也最容易被「靜電釋放(ESD)」或其它場感應,變成一個天線。多層堆棧的PCB可以減輕ESD的破壞,並能減少磁場的產生,避免它輻射至自由空間。在附圖七中,接地平面和電源平面之間,具有一個很小的迴路面積。

使用電源和接地平面可以降低電源分配系統的電感值。若將電源分配系統的特性阻抗降低,則可以降低電路板的電壓降。電壓降若變小,則「接地彈跳(ground bounce)」的現象就可以避免。當邏輯閘開關快速切換時,瞬間的電流變化會經由IC接腳,傳送至主機板的電源平面或接地平面,造成輸入參考電壓的波動,進而產生射頻雜訊(RF noise)和電磁干擾,這種現象就稱作「接地彈跳(ground bounce)」。此外,降低特性阻抗的同時,電源平面與接地平面之間的電容值會增加,這個電容值會使得任何的感應電壓值下降,這就是「去耦合(decouple)」的效果。

圖六:綠色區域是大的迴路面積

當訊號線在組件之間穿梭時,大的迴路面積就被產生了。但是我們常常會忘記訊號線對EMI的影響。雖然,訊號的完整性(時域)仍然很高,但是,EMI 依然存在(頻域),因為訊號迴路面積所產生的問題,比電源分配系統所產生的問題多。尤其是從ESD的觀點來分析,更是如此;這是由於ESD會直接進入迴路和組件的輸入腳位中。為了降低ESD可能造成的傷害,減少迴路面積是最簡單的方法。電源和接地平面分散網路提供了低阻抗的路徑,能夠將ESD能量傳送至 0V的回傳參考平面內。畢竟,迴路是迴路,如果它們能發出電磁波,就應該能夠接收電磁波。

除了能降低接地雜訊電壓以外,映像平面也能防止射頻接地迴路變大,因為射頻電流緊密地與它們的電流源走線耦合,所以,它不需要另外尋找回傳路徑。當迴路控制最大化時,磁通量就被大幅消除了。這是在PCB內,抑制射頻電流的最重要觀念之一。在靠近每一個訊號平面處,正確地配置映像平面,就可以消除共模的射頻電流。傳輸大量的射頻電流的映像平面,必須接地或接至0V參考點。為了移除多餘的射頻電壓和渦流,所有接地和底座平面可以透過一個低阻抗的接地電路,連接至底座的接地點。

圖七:具有一個很小的迴路面積的PCB布線

接地線的間距

要降低PCB內的迴路生成,最簡單的方法是設計許多個接地線,並全部連接至底座的接地點。由於組件的輸出訊號的邊緣速率(edge rate)加快了,所以,多點接地就變成了必要的規格,尤其當有使用到I/O互連的設計時。當PCB使用多點接地,而且都連接到一個金屬結構上,這時,我們必須知道所有接地線之間的間距是多少。

接地線之間的距離不能超過最高頻率的λ/20,這不僅包括主頻率,也包含諧波頻率。如果某組件的輸出訊號的邊緣速率比較慢,則它連接至底座接地點的數目可以減少,或和接地位置的距離可以增加。例如:一個64MHz的振蕩器的λ/20是23.4公分,若兩個接地線的直線距離大於23.4公分,則很可能會有射頻迴路存在,這個迴路可能就是射頻能量傳播的來源。

在PCB中的組件布局必須要正確。將不同功能區塊的接地線緊密相鄰,可以縮短訊號走線的長度、降低反射、並使繞線容易,同時保持訊號的完整性。應該要盡量避免使用通孔(via),因為每一個通孔會增加走線的電感值大約1至3 nH。

此外,為了防止不同的頻寬區域相互耦合,必須對不同的功能區塊做正確的分割(partition),其方法有:使用分離的PCB、絕緣、不同的布線….等。正確的分割可以提高電路效能、使繞線容易、縮短走線的長度,並且能縮小迴路的面積、提升訊號質量。工程師在布線之前,必須先規劃好哪些組件是屬於哪一個功能區塊,而這些信息可以從組件供貨商處獲得。

[admin via 研發互助社區 ] EMI/EMC設計(四)印刷電路板的映像平面已經有5802次圍觀

http://cocdig.com/docs/show-post-44285.html