無論在何種情況下,兩個具有不同電位的導體間都會產生電容。在兩個具有不同電位的導體之間,總是存在一個電場。電場中存儲的能量由驅動電路供給。因為驅動電路是一個功率有限的激勵源,所以在任何兩個導體之間的電壓將在有限的時間內建立一個穩定狀態值。隨著能量的注入,電壓會很快地建立或衰減,其中對電壓的阻力稱為電容。例如兩個平等金屬板的結構,在低電壓下包含了大量電荷,所以電容就很大。

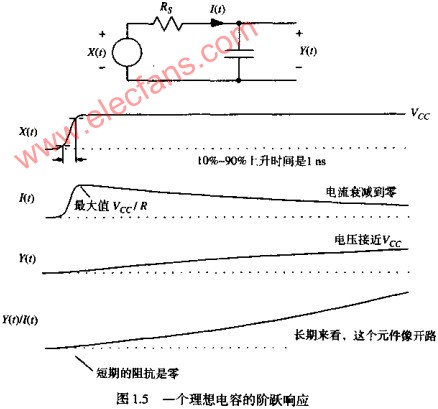

圖1.5顯示了由30歐激勵源驅動一個電容時理想的電流和電壓波形,電容階躍響應的上升變化顯示為一個時間的函數。當電壓階躍剛開始時,大量的能量流入電容,從而建立起它的電場。進入電容的初始電流相當高,而電壓階躍剛開始時,大量的能量流入電容,從而建立起它的電場。進入電容的初始電流相當高,而電壓與電流的比值Y(T)II(T)非常低。在很短的時間範圍內,電容看起來就像一個短路連接。

隨著時間的推移,比值Y(T)II(T)逐漸增大。最終,電流下降至接近於零,電容此時看起來像開路一樣。最後,電容內的電場完全建立,由於電介質非理想的絕緣性質,電容兩極之間只有一個很小的泄漏電流存在。此時的Y(T)II(T)比值非常高。

有此電路元件的階躍響應在某個時間範圍內顯示為電容特徵,而在另外的時間範圍內顯示為電感特徵,或者相反,舉例來說,電容的安裝引腳在非常高的頻率時,其電感通常足以使整個元件呈現為電感特徵。該電容的階躍響應在零時刻會出現一個微小的脈衝,也許僅有數百皮秒(對應於引腳電感大小),接著下降至零,隨後才是一個正常的容性上升斜線。

如果階躍激勵源的上升時間太慢,輸出曲線的軌跡將不會出現電感性尖脈衝。由於脈衝非常短,如果示波器的掃描時間基準設定得太慢,也很容易會錯過。令人感興趣的是,通過調整上升時間和設定掃描時間基準,我們可以使電路元件的階躍響應測量結果在某個特定頻率範圍內特徵更加突出。概括來說,如果階躍上升時間是TR,接近零時刻的階躍響應與電路元件在頻率FA附近的阻抗大小有關:FA=0.5/TR

其中,TR=階躍激勵源的上升時間

FA=近似分析頻率

通過直觀地平均整個時間周期上的階躍應值,我們可以休息出較低頻率上的阻抗大小。採用上式可以計算出應於一個平均周期值TR的近似分析頻率。

階躍響應的最終數值顯示出了直流時的阻抗。

僅從一個階躍上升時間TR,我們無法推斷出比FA更高的頻率分量上更多特性。只有階躍激勵源的信號頻率足夠高,才能確保揭示出所想要看到的情況。

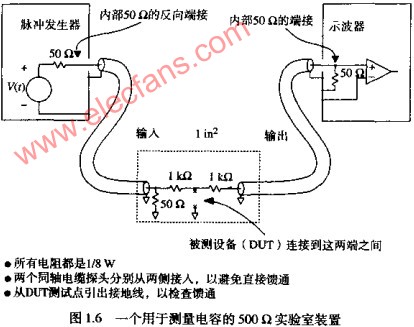

圖1.6描繪了一個測量裝置,適合用來表現一個幾皮法電容在納秒級時間周期上的特性。這個裝置適用於揭示諸如印刷電路走線、六電路輸入電容、旁路電容元件以及其他數字電路通用元件的電容特性。該方法通過一個已知的電阻來驅動被測電容。通過測量產生波形的上升時間,可以推導出電容的容值。與音頻電路所用技術相比較,這個裝置非常複雜。複雜性來自於在高頻電磁場能量的控制和引導方面的困難。同軸電纜用來直接引導測試信號,並把測量結果輸入輸出到一個小於1IN的完整地平面,該處是實際進行測量的位置。把測量區域限制為NIN,是為了確保電路呈現為集總電路的特性。

例1.1 一個小的接地電容的測量

本例中(見圖1.6)的被測設備(DUT)是一個平行板電容器。採用0.5IN*0.75IN的1.5IZ覆銅印製在環氧樹脂FR-4印刷電路板正面,背面是一個平行的完整地平面,標稱的平行間隔為0.008IN。這個結構一個電容器,附帶有非常低的寄生串聯電感。

測量裝置由兩個RG-174同軸電纜組成,分別用於信號的輸入和輸出。輸入電纜通過50歐端接到地,已端接的信號輸出通過一個1K的驅動電阻連接到被測設備。1K電阻隔離了被測設備與信號源,為信號幅度性能的一致性,面無需考被測設備的負載阻抗。

實際路中的信號源脈衝發生器應能提供幅度及上升時間與期望相近似的信號。當測量無源元件時,脈衝發生器的直流偏置不太重要。另一方面,當測量門電路輸入時,通常應使脈衝源的輸出覆蓋門電路輸入的整個轉換範圍,並向被測門電路提供能量,以使門電路偏置於實驗所需的工作範圍之內。需要較大輸入驅動電流的門電路可能還會要求比1K更小的源端電阻。

如果信號發生器具有一個50歐的反端接器件,利用它可以減少輸入電纜上的反射。該器件在信號發生器輸出級插入一個50歐的串聯阻抗,可以減少信號源電纜的前向和反向反射,該反射通常是由測試夾具與信號源輸出阻抗之間不可避免的輕微不匹配而引起的。反向端接后,來自源信號的不必要反射被兩次衰減,第一次是被測試夾具彈回時,第二次是在源端反向端接電阻上反彈后返回到測量儀器的路徑上,反向端接雖然使信號源輸出的有效幅度降低了一半,但是改善了系統階躍響應。

輸出電纜通過一個1K電阻與被測電路隔離連接,另一端連到一個內部含有50歐端接的示波器輸入端。1K電阻起一個21:1探頭的作用。這裡的輸入和輸出電纜都是3FT長。

輸出電纜通過一個1K電阻與被測電路隔離連接,另一端連到一個內部含有50歐端接的示波器輸入端。1K電阻起一個21:1探頭的作用。這個信號感應裝置的優點將在本書後面關於示波器探索測的小節中詳細闡述。這裡的輸入和輸出電電纜都是3FT長。

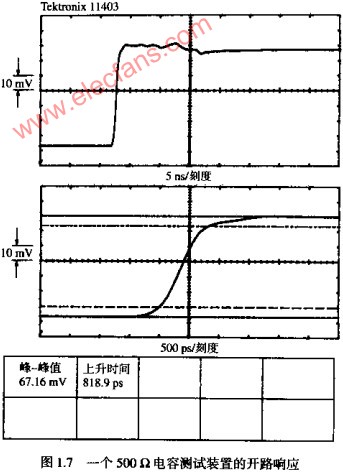

當信號源的階躍輸入為2.6V,且DUT斷開時,這個探頭的開路響應結果如圖1.7所示。頂部的掃描線是以5NS/刻度記錄的,底部的掃描線記錄的是同一信號放大為500PS/刻度的視圖。

用於記錄這個波形的TEKTRINIX11403示波器自動計算出的10~90%上升時間為818PS標稱階躍幅度的1/21,而DUT上幅度1.3V是信號源驅動電壓的一半。

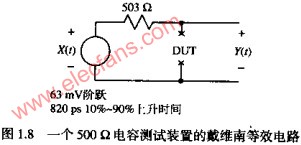

如圖1.8所示,這個實驗配置的戴維南等效電路,將總系統上升時間都集中表現到信號源上。這裡不關心究竟是信號源還是示波器使得觀察到的上升的時間變得更慢。任何一個具有近似開路的時間的信號源與示波器的合理組合,在這個DUT的影響下都會有類似的特性。我們只關心已知的信號源-示波器的合理組合,在這個DUT的影響下都會有類似的特性。我們只關心已知的信號源-示波器組合的總上升時間。當測量無源元件時,我們同樣只關心觀察到的階躍幅度,而DUT上實際的電壓細節的探頭衰減比例都不重要。

關掉脈衝源而仍然保持50歐反向端接的連接,採用一個歐姆表在DUT的端子上測量,得到信號源的源端阻抗為503歐。這個503歐電阻是1K驅動電阻和1K感應電阻關聯的結果。

在連接DUT的情況下,觀察到的電壓波形顯示為電容特性,由低開始然後上升。初始驅動波形的存儲副本被重疊在這個圖上以便讀者參考。通過這個探頭,在整個可觀察的時間刻度範圍上,從800PS(信號源和示波器組合的總上升時間)到40NS(在示波器圖中顯示的線跡長度),DUT表現出理想的容性。

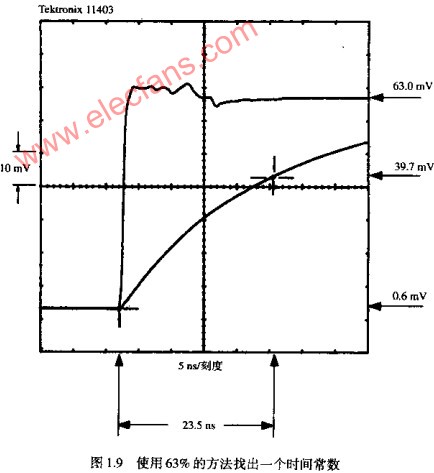

從圖1.9中游標沿著上升時間標出的63%的點,我們可以得知RC時間常數時間常數為23.5NS。已知驅動電阻為503歐,我們可以用關係式C=π/R計算出DUT的電容值:

從這個上升時間的頻率之間的關係可以推導出一個粗略的辦法,用電容的數字波形前沿來表示電抗。當考慮到由於一個容性負載導致的數字波形失真時,這種方法非學有用。

XC=T1/XC

對於一個3NS上升沿。例1.1中的電容的電抗值為20.44歐,由此我們預知它將會使來自輸出阻抗為30歐的TTL驅動器的一個3NS上升沿顯著畸變。

在任何時刻,電容上升過的電流與其電壓的上升時間的關係總是依照下列通用公式:

I電容=C DV電容/D1

[admin via 研發互助社區 ] 線路電容原理與計算已經有7547次圍觀

http://cocdig.com/docs/show-post-39000.html