電流源及電流源驅動器的應用

電流源輸出電路具有線性的優勢,通常在一些專門的總路線應用中採用。當驅動一個長的匯流排時,其電流輸出自然而然地相互疊加,與電壓源輸出中非線性方式的相互影響形成鮮明對比。

由於這些電路被設計線性甲類放大器,驅動晶體管工作在非飽和狀態,因而輸出電路消耗大量的能量。

集電極開路驅動電路或者在電流很大時壓降很小,或者在壓降很大時幾乎沒有電流。兩種狀態消耗的能量都很少。與之相反,電流源驅動器在一個或多個狀態中有時壓降大而電流也大。儘管能量利用效率不高,但電流源輸出電路在長匯流排結構中還是具有很大的優勢。例展示了使用電流源驅動器的一大好處。

例:電流源驅動器的應用

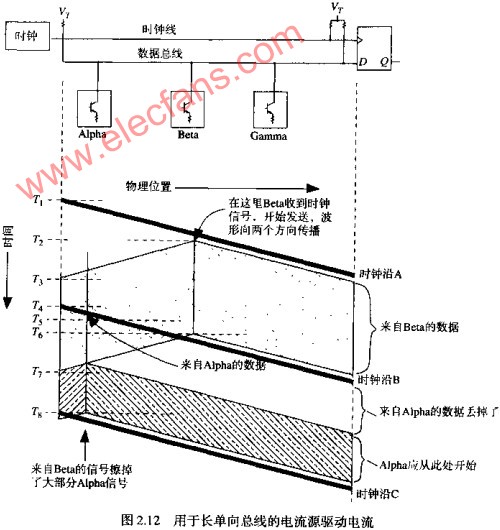

某些系統使用電流源驅動器構成一個單向匯流排(見圖2.12)。時鐘驅動器分別從T1、T4和T8時刻開始劃分了一連串的時鐘間隔。時鐘信號從左到右與數據匯流排并行傳播,匯流排驅動器分別被命名為A1PHA、BETA和GAMMA,負責在預定的時隙把數據輸入到匯流排。發射器件上的總路線發送時間與時鐘信號到達的時間一致。這樣的安排保證每個數據單元在正確的時鐘間隔區間里到達匯流排的右端,而不管它在匯流排上被發送時的物理位置。僅有的一個接收器位於匯流排的右端隨著到達的時鐘信號同步地將匯流排上的數據信號鎖存。

圖2.12顯示了兩個數據單元,第一個由BETA發出,第二個由ALPHA發出,BETA在T2時刻開始發送,然後在一個時鐘間隔后的T6時刻停止,這一時間與時鐘信號A和B到達BETA處的時間相一致。同樣,在時鐘信號到達的T5時刻ALPHA開始發送,一個時鐘隔后停止。

當每個器件發送數據時,它的信號沿著數據匯流排同時向左右兩個方向傳播。在數據總路線的右端,兩個信號嚴格地終止於各自的指定時隙。

到目前為止,這裡對該匯流排的運行速度還沒有做理論上的限制。由於我們不必等待時鐘向下傳輸並從遠端返回,所以可以提高時鐘速率至任意的頻率,只受限於相關器件的工作速度,而不是匯流排的物理傳播速度與長度。匯流排可以同時傳送多個傳向右側接收器的數據單元。

這種單向匯流排的問題至於,我們只關心了傳向匯流排右側的信號,然而實際上發送的信號是同時向兩個方向傳播的。研究一下T2時刻BETA發送信號時的情況,它發送的信號傳向右側(接收器方向)的同時也朝相反方向的ALPHA傳播。在T5時刻,當ALPHA要啟動發送的時候,來自BETA的數據A的後半部分正在通過數據匯流排。

如果發送器ALPHA是一個推拉輸出驅動器,並且數據A的值和數據B相同,那麼在數據B完全通過之前不會有來自ALPHA驅動器的電流流過數據匯流排。此時,數據匯流排已經處在所要的邏輯狀態,因此發送器ALPHA對匯流排沒有影響,就好像ALPHA沒有被連接到匯流排一樣。一旦數據B完全通過,在T7時刻,推拉輸出驅動器ALPHA開始輸出電流,以使匯流排保持在既定的狀態。在接收端,由於直到完全進入ALPHA所分配的時隙之後還沒有從ALPHA發送的信號波到來,所以數據B的前端部分沒有接收到。

同樣,如果數據A和B正好相反,ALPHA必須用兩倍的輸出來驅動匯流排,於是數據B的前端部分在接收器輸入端D會呈現出一個超常的大脈衝。

解決這個問題的辦法是使用線性驅動電路,無論匯流排上當前是什麼狀態,它都能疊加上自己的信號。正確的電路結構應該是電流源,通常是用集電極開路和漏極開路電流調整電路來實現。這類電路將預定數量的電流注入數據匯流排。數據匯流排的響應如同一個阻性負載,產生一個相應的電壓偏移。兩個邏輯狀態中的一個通常被設定為零電流,未激活的器件處於這個狀態。

根據總路線的長度,每個驅動器都可能工作在多個數據同時經過的情況,每個數據分別來自位於電纜不同位置的驅動器。這一要求意味著驅動器必須在很寬的電壓範圍上提供線性的電流。在很寬電壓範圍上提供恆定驅動電流將會超耗費大量的功率。

[admin via 研發互助社區 ] 電流源及電流源驅動器的應用已經有5243次圍觀

http://cocdig.com/docs/show-post-38998.html