一、什麼是DDS?

Direct digital synthesis(DDS)是一種產生模擬波形的方法。通常是通過數字形式的時間轉換信號再執行數模轉換產生正弦波。因為DDS設備上運行是基於數字,所以能夠在輸出頻率、正弦波頻率分解和運行於寬頻率頻譜之間相互轉換。由於設計優勢和處理技術,如今的DDS設備十分簡潔而且低功耗。

二、為什麼要使用DDS?有沒有其它簡便方法產生頻率?

精確產生和控制各種頻率的波形和輪廓的能力變成關鍵必需條件是很多工業方面的共識。下面是一些設計的重要考慮因素:是否提供優秀性能可用於通訊方面的、方便的低相噪,可變頻率的波形、用於工業方面的簡單產生頻率、生物測試設備應用,方便的工具機械等等。

許多頻率產生的可能方案對工程師開放,範圍從基於PLL技術的高頻合成到動態可編程DAC輸出產生低頻時任意波形。但是DDS技術能解決通訊和工業方面頻率產生應用,因為單片集成IC設備能產生可編程模擬輸出的高性能和精度波形。它在這兩個方面很快獲得了接受。況且,在處理技術和設計方面連續的改進導致了價格和功耗級別達到了以前無法想象的地步,比如:AD9833,一個基於DDS的可編程波形產生,在25MHz時鐘和5.5V下工作的最大功耗才為30mW。

三、用DDS的最大好處是什麼?

像AD9833的DDS是可編程的通過高速串口外圍介面(SPI),只需要一個外部時鐘去產生簡單正弦波就可工作。DDS設備現在能夠在基於1GHz的時鐘下產生低於1Hz到400MHz的波形,它低功耗,廉價,小封裝,聯合內部的優良性能和對輸出波形數字可編程能力,使DDS設備比起由分立元件組成的低靈活性的方案來說是極其有吸引力的解決方案。

四、典型的DDS設備能產生什麼種類的波形?

DDS設備不僅僅局限於純粹的正弦波輸出,比如:AD9833可輸出正弦波,方波和三角波。

五、DDS設備如何產生正弦波?

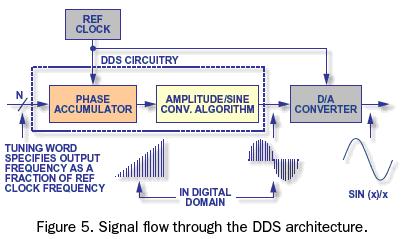

下圖是一個DDS設備內部電路的細目分類:它主要由一個相位積聚者,一個相位振幅轉換方法和一個DAC。一個DDS產生一特定頻率的正弦波,頻率取決於兩個可變參數:參考時鐘頻率和寫進頻率寄存器的可編程二進位數(調諧命令)。

寫進頻率寄存器的二進位數提供主要輸入到相位積蓄者,如果正弦波查詢表用了,相位積蓄者為查詢表估算相位地址,輸出振幅的數字值-----對就於正弦波的相位-----送到DAC,依次轉換模擬電壓或者電流的相信值的數值,去產生可變頻率正弦波,(相位增量由二進位數決定)一個連續值在各自的時鐘周期被加到相位積蓄者。如果相位增量大,相位積蓄者將通過正弦查詢表加快所以產生高頻率正弦波。如果相位增量小,相位積蓄將經過更多步驟,因此產生較慢的波形。

六、你對完全的DDS如何定義?

一個DAC轉換和一個DDS集成到一塊晶元上就是我們通常所了解到的完全的DDS。

七、讓我們再談談相位積蓄者,它是如何工作的?

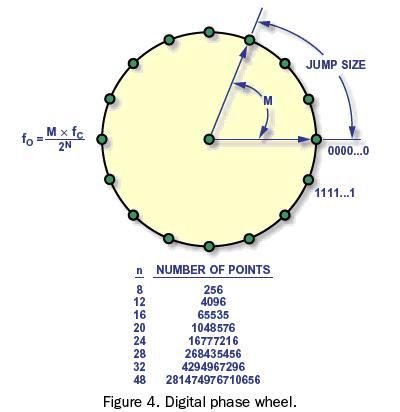

連續正弦信號有一個反覆的範圍在0到2的角度相位。但在數字執行時沒有什麼不同,計數器執行功能時允許相位積蓄者在DDS執行時作為車輪一樣逐步採用。

為了明白這一基本功能,我們想象正弦波作為一個矢量旋轉式噴頭繞羊相位圓振動。每個相位輪上的指定點對應於正弦波周期上的等價點。因為矢量圍繞輪轉動,想象正弦波的角度產生對應的正弦波輸出。一次矢量以恆定速度圍繞相位圈旋轉,就產生了一個完整周期的正弦波輸出。相位積蓄者提供相等空間的有效值伴隨矢量繞相位圈的線性旋轉。相位積蓄者裡面的內容就對應於輸出正弦波周期上的點。

相位積蓄者實際是以計數器為模的,當每次接收到時鐘脈衝時它就增加它的存儲值。它的增加值由二進位代碼輸入命令(M)決定。這個命令使相位增加範圍在參考時鐘之間;它有效地設置在相位圈上跳躍多少點。跳躍尺碼越大,相位積蓄者溢出和完成相等正弦波周期就越快,輪上包含的不連續相點的數目由積蓄者(n)決議決定的,它決定DDS的調諧決議,因為n=28-相位積蓄者的位,若M值為0000...0001,那麼相位積蓄者會在2*參考時針周期(增量)后溢出。若M的值變為0111...1111,相位積蓄者將只在兩個參考時鐘周期后便溢出,(最小需求由Nyquist(翻譯不出來))。這種關係在DDS體系結構的基本調諧平衡中可以找到。

Fout=M*fc/2^n

註:Fout為DDS輸出頻率

M為二進位調諧命令

Fc為內部參考時鐘命令

N為相位積蓄者的長度(按位)

改變M的值會直接導致輸了頻率相位的直接改變,由於鎖相環的存在,沒有帶來任何循環處理滯后時間。由於輸出頻率增加,所以每個周期的採樣數目將減少。正弦抽樣法理論規定:為了重新建立輸出波形,每個周期到少要兩個採樣,DDS最大的基本輸出頻率是fc/2。但是,是實際應用的時候,輸出頻率多多少少有一些限制,比理論值要少一些,可以改進重建波形的質量,輸出濾波。當產生恆定的頻率時,相位積蓄者的輸出是線性增加的,所以模擬波形的產生是一個固有的斜坡。

八、那麼它的線性輸出又是如何轉化為正弦波輸出的呢?

一個相位轉振幅的查找表用於轉換相位積蓄者的即時輸出值(AD9833是28位),它切斷不需要的無效位,進入在D/A轉換器(10位)中的波形振幅信息。DDS應用正弦波對稱的性質,它從相位積蓄者中的四分之一的正弦波波形中邏輯映射出一個完整的波形,相位轉振幅查找表通過讀和轉寄產生保持的數據再通過查找表返回。如圖:

九、DDS最受歡迎是用在哪些方面?

基於DDS波形產生的應用現階段主要在兩個方面:1、設計通訊系統需要靈活的和極好的相噪,極低的失真性能的頻率源,它通常選用DDS結合它的光譜性能和頻率調諧方案,

這種應用包括用DDS於調製方面,作為PLL參考去加強整個頻率的可調製度,作為本機振蕩器(LO),或者射頻率的直接傳送。作為選擇地,許多工業和醫學應用DDS作為可編程波形發生器。因為DDS是數字可編程,它的相位和頻率在不改變外圍成分的情況下能很容易地改變,而傳統的基於模擬編程產生波形的情況下要改變外圍成分。DDS允許頻率的實時調整去定位參考頻率或者補償溫度漂移。這種應用包括應用DDS在可調整頻率源去測量阻抗(比如:基於阻抗的感測器),去產生脈衝波形已調製信號用於微型刺激,或者去檢查LAN中的稀薄化和電纜。

你認為DDS用於現實中的設備和系統中有什麼關鍵的優勢?

如今在價格方面有竟爭力的,高性能,功能集成的DDS晶元在通訊系統和感測應用方面已經變得非常常見了。它吸引工程師的優勢主要包括:

*數字控制微調頻率調諧和輕微程度相位調製能力。

*極快速度調諧輸出頻率(相位);在沒有上沖或者下沖的請況下,且沒有延時的情況下可以進行連續頻率調諧。

*DDS的數字體系結構取消了像傳統模擬合成方案那樣的手動調諧和溫度補償方面的不方便,DDS的數字控制結構外圍便系統的遠程控制更為方便,在處理器控制下達到最優化。

十、我如何用DDS設備用於PSK編碼?

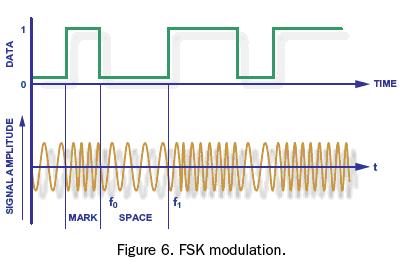

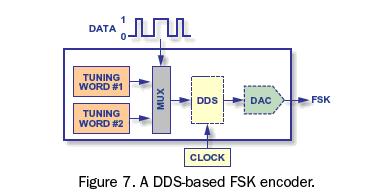

二進位頻率轉換鍵控(通常簡化為FSK)是數據編碼的最簡單形式之一。數據由轉換連續載波頻率去一個或者兩個離散的頻率(所以二進位),一個頻率f1(也許是較高的那個)指定為標誌頻率(二進位的位1),而另一個頻率f0,作為space frequency(二進位的位0),圖六舉出了脈衝間隔數據和轉換信號之間的關係。

用DDS實現編碼方案很容易實現。DDS的頻率調諧命令,設置適當的值當它們發生在模式0和1即將傳送時去產生fo和f1,體現在輸出頻率上。在傳送之前用戶可以編程兩個必需的調諧命令到設備,當用AD9834時,兩個頻率寄存器去產生方便的FSK代碼是可行的。IC上一個專門的引腳(FSELECT)接收調製信號選擇適當的調諧命令(或者頻率寄存器)。圖七展示了簡單的FSK編碼的執行:

十一、那麼PSK解碼呢?

周相移動鍵控(PSK)是另一數據編碼的簡單形式。在PSK中,載波的頻率恆定,而發送信號的相位改變去傳達信息。

完成PSK的方案中,最簡單易知的是BPSK,即只用兩個信號相位:0度和180度。BPSK編碼0周相移動作為邏輯1輸入,而編碼180周相移動作為邏輯0輸入。每一位的狀態由前述位的狀態決定。當波形相位不變時,信號狀態也保持不變(高或者低)。當波形的相位翻轉(改變180度),信號狀態就會改變(低變高或者高變低)。

PSK編碼很容易用DDS晶元實現,許多設備含有獨立的能夠取相位值的輸入寄存器(相位寄存器)。這個值在不改變載波頻率的情況下加到載波相位,改變這個寄存器中的的內容去調節載波相位,因此產生了PSK信號輸出。因為應用需要高速調製,AD9834用一個專門的toggling輸出腳(PSELECT)去選擇預載寄存器,如果需要它在寄存器和載波調製之間交替著。

許多複雜形式的PSK需要四個或者八個波動相位。這就說明了二進位數比起BPSK調製來說,在每個相位中傳遞得更快了。四相位調製(QPSK)中,可能相位角是:0度,+90度,-90度和180度;每個相位轉換能夠展現兩個信號元素。AD9830, AD9831, AD9832和 AD9835提供了四相位寄存器供給複雜相位調製方案,它由連續更新寄存器中不同相位偏差來實現。

十二、多片DDS晶元能不能夠同步?也就是說I-Q能力?

當兩片DDS設備設備運行在相同的主時鐘時,輸出的兩個信號的相位關係能夠直接控制是可能的。在例8中,兩片AD9834用同一個參考時鐘,同一個複位腳去更新兩片IC。在這種情況下,可以實現I-Q調製。

當上電後進行轉換任何數據的時候DDS必須進行複位。這使DDS輸出的波形相位已知,這為多片DDS設備同步以共同參考點的形式提供。當新的數據同時送到多片DDS單元,能夠保持一個連貫的相位關係,它們的相對相位編移量能夠通過相位編移寄存器預先轉移。The AD9833 and AD9834有12位的相位分辨能力,它能夠有效地分辨到0.1度。[DDS的同步應用更詳細資料見應用筆記AN-605。]

十三、一個基於DDS的系統最關鍵的性能規格是什麼?

相位雜訊,顫動,純動態範圍(SFDR)

相位雜訊是振蕩器的短期頻率不穩定度的測量標準(dBc/Hz)。它測量由改變兩個或者多個從振蕩器的工作頻率的轉換而引起的單邊帶雜訊來衡量的(用1Hz寬頻來測量振蕩器工作頻率下低于振幅的分貝值。)。這種測量在模擬通訊領域有著特殊的應用。

十四、DDS設備有良好的相位雜訊嗎?

雜訊是一種取決於很多因素的樣品系統。在DDS系統中在基本信號中參考時鐘的顫抖可以看作是相位雜訊;相位切斷可能包括系統內的錯誤,取決於選擇的代碼字。因為比率能夠由刪去了的二進位代碼值很精確地表現,這沒有任何截斷誤差。因為比率需要比現存更多的位,由於光譜結構它產生了相位雜訊截斷誤差。它的數量和公布取決於選擇的代碼字。系統中的DAC也提供了雜訊。DAC的量子化和線性誤差導致了雜訊和失真。圖九顯示了典型DDS系統---AD9834中的相位雜訊帶。

十四、什麼是顫動?

顫動是數字信號從它們長期平均位置來說的動態位移,用單位rms來測量。一個良好的振蕩器在剛好的時機有它的上升沿和下降沿而不會改變。這當然是不可能的,因為即使最好的振蕩器在構建的時候了包含了雜訊源和非理想性。一個高質量、低雜訊的晶體振蕩器每周期振動可達到35皮秒(ps),累積斷百萬個時鐘邊沿。

振蕩器的振動是由於熱噪引起的,振蕩不穩定性或者電氣,通過電源軌或者地和輸出聯接的外部干擾。其它影響包括外部電氣或者外磁鐵,比如:附近的發射機的射頻干擾,它能夠產生顫動影響振蕩器的輸出。即使一個簡單的放大器,轉換器,或者緩衝器也將給信號帶來顫動。

DDS設備輸出將帶上一定程度的顫動。因為每個時鐘將已經有內在的顫動,選擇低顫動的時鐘是必須的,降低高頻時鐘的頻率也是減小顫動的一個方法。降低頻率后,相同數量的顫動發生在更長的周期內,降低了百分率。

一般而言,減少必要的顫動源和消除引進額外源,一個必要用穩定的參考時鐘,避免用低速的信號和電路,用最高速可行的頻率去允許增加的取樣。

十五、純動態範圍

In general, to reduce essential sources of jitter and avoid introducing additional sources, one should use a stable reference clock, avoid using signals and circuits that slew slowly, and use the highest feasible reference frequency to allow increased oversampling.

Spurious-Free Dynamic Range (SFDR) refers to the ratio (measured in decibels) between the highest level of the fundamental signal and the highest level of any spurious, signal—including aliases and harmonically related frequency components—in the spectrum. For the very best SFDR, it is essential to begin with a high-quality oscillator.

SFDR is an important specification in an application where the frequency spectrum is being shared with other communication channels and applications. If a transmitter’s output sends spurious signals into other frequency bands, they can corrupt, or interrupt neighboring signals.

Typical output plots taken from an AD9834 (10-bit DDS) with a 50-MHz master clock are shown in Figure 10. In (a), the output frequency is exactly 1/3 of the master clock frequency (MCLK). Because of the judicious choice of frequencies, there are no harmonic frequencies in the 25-MHz window, aliases are minimized, and the spurious behavior appears excellent, with all spurs at least 80 dB below the signal (SFDR = 80 dB). The lower frequency setting in (b) has more points to shape the waveform (but not enough for a really clean waveform), and gives a more realistic picture; the largest spur, at the second-harmonic frequency, is about 50 dB below the signal (SFDR = 50 dB).

[admin via 研發互助社區 ] 關於DDS的一些問題已經有4193次圍觀

http://cocdig.com/docs/show-post-44724.html