1 引言

近年來,隨著攜帶型數字電子產品筆記本計算機、數字式行動電話、手持式測試儀錶等的迅速發展,要求使用體積小、功耗低、電池耗電小的器件,數字系統的工作電壓已經從5V降至3V甚至更低(例如2.5V和1.8V標準的引進)。但是目前仍有許多5V電源的邏輯器件和數字器件可用,因此在許多設計中3V(含3.3V)邏輯系統和5V邏輯系統共存,而且不同的電源電壓在同一電路板中混用。隨著更低電壓標準的引進,不同電源電壓邏輯器件問的介面問題會在很長一段時間內存在。本文討論的是使用TTL和CMOS的3V和5V系統中邏輯器件間介面的基本概念和電路實例。理解了這些概念可避免不同電壓的邏輯器件介面時出現的問題和保證所設計的電路數據傳輸的可靠性。

2 邏輯電平不同,介面時出現的問題

在混合電壓系統中,不同電源電壓的邏輯器件相互介面時會存在以下3個主要問題:

器件對加到輸入腳或輸出腳的電壓通常是有限制的。這些引腳有二極體或分離元件接到Vcc。如果接入的電壓過高,則電流將會通過二極體或分離元件流向電源。例如3V器件的輸入端接上5V信號,則5V電源將會向3V電源充電。持續的電流將會損壞二極體和電路元件。

在等待或掉電方式時,3V電源降落到0V,大電流將流通到地,這使匯流排上的高電壓被下拉到地,這些情況將引起數據丟失和元件損壞。必須注意的是:不管是在3V的工作狀態或是0V的等待狀態部不允許電流流向Vcc。

另外用5V的器件來驅動3V的器件有很多不同情況,同樣TTL和CMOS間的轉換電平也存在不同情況。驅動器必須滿足接收器的輸入轉換電平,並要有足夠的容限和保證不損壞電路元件。

以上問題在詳細地分析一些具體電路后便會很清楚。

3 可用5V容限輸入的3V邏輯器件

3V的邏輯器件可以有5V輸入容限的器件是LVC、LVT、ALVT、LCX、LVX、等系列。此外,還有不帶匯流排保持輸入的飛利浦ALVC器件也是5V容限。

3.1 ESD保護電路

為了說清楚為什麼3V器件可以有5V的輸入容限,首先介紹邏輯電路輸入端的靜電放電(ESD)保護電路的工作原理。

實際上數字電路的所有輸入端部有一個靜電放電(ESD)保護電路,如圖1(a)所示。傳統的CMOS電路通過接地的二極體D1、D2對負向高電壓限幅而實現保護,正向高電壓則由二極體D3鉗位。這種電路的缺點是為了防止電流流向Vcc電源,最大的輸入電壓被限制在Vcc+0.5V。對Vcc為3V的器件來說,當輸入端直接與大多數5V器件輸出端介面時允許的輸入電壓會太低。大多數5V系統加到輸入端的電壓可達3.6V以上。有些3V系統電路可以使用兩個MOS場效應管或晶體管T1、T2代替圖1(a)中的D1、D2二極體,如圖1(b)所示。T1、T2的作用相當於快速齊納二極體對高電壓限幅。由於去掉了接到Vcc的二極體D3,因此最大輸入電壓不受Vcc的限制。典型情況下,這種電路的擊穿電壓在7-10V之間,因此可以適合任何5V系統的輸入電壓。

(a)傳統的ESD保護電路,輸入電壓被限制在Vcc+0.5V

(b)改進的ESD保護電路,輸入電壓不受Vcc限制

圖1 CMOS ESD保護電路

由上分析可知,改進后具有ESD保護電路的3V系統的輸入端可以與5V系統的輸出端介面。

3.2匯流排保持電路

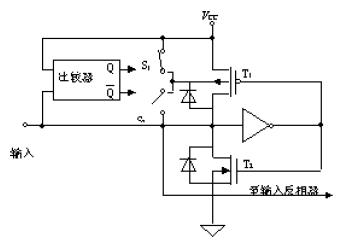

匯流排保持電路就是有一個MOS場效應管用作上拉或下拉器件,在輸入端浮空(高阻)的情況下保持輸入端處於最後有效的邏輯電平。圖2(a)中的電路為一LVC器件匯流排保持電路的例子。在該例子中製造商採取了改進措施而使其輸入端具有5V的容限。其基本原理如下:P溝道MOS場效應管T1具有一個內在的寄生二極體,它連接在漏極和襯底之間,通常源極與襯底是連在一起的,這就限制了輸入電壓不能高於Vcc+0.5V。現在的措施是用常閉接點S1將源極與襯底相連,當輸入端電壓比Vcc高0.5V時,比較器使S2閉合,S1斷開,輸入端電流不會通過二極體流向Vcc而使輸入具有5V的容限。圖2(b)是LVT和ALVT器件匯流排保持電路的例子。這種電路用了一個串聯的肖特基二極體D,這樣就消除了從輸入到Vcc的電流通路,從而可以承受5V輸入電壓。對於3V的匯流排保持LVC、LVT和ALVT系列器件可以承受5V的輸入電壓。但對於3V的ALVC、VCX等系列器件則不能,它們的輸入電壓被限制在Vcc+0.5V。

(a)在LVC匯流排保持電路中,當輸入電壓上升超過Vcc時,比較器使S1開路,消除了至Vcc的電流通路

(b)LVT和ALVT器件,反向偏置的肖特基二極體斷開了到Vcc的電流通路

圖2具有匯流排保持電路的輸入端

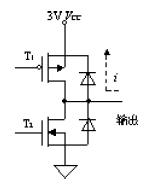

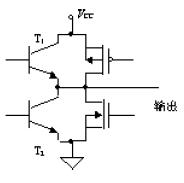

下面討論輸出端的情況。圖3是用於3V CMOS器件的輸出電路的簡化形式。當輸出端電壓高於Vcc 0.5V(二極體壓降)時,P溝道MOS場效應管T1的內部二極體會形成一條從輸出端到Vcc的電流通路。所以這種電路在與5V器件相接時需要加保護電路。

圖3簡化的CMOS輸出級

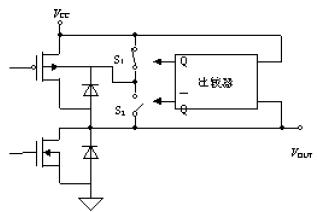

圖4是一種帶保護電路的CMOS器件輸出電路。當輸出端電壓高於Vcc時,比較器使S1開路,S2閉合,使電流通路消失,這樣在三態方式時就能與5V器件相接。

圖4帶保護電路的CMOS輸出端

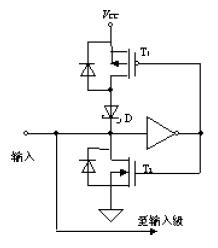

3.3 biCMOS輸出電路

LVT和ALVT器件的biCMOS輸出電路如圖5所示。它用雙極NPN晶體管和CMOS場效應管來獲得輸出電壓擺幅達到電源電壓的要求。電流不會通過NPN雙極晶體管T1迴流到Vcc,但在P溝道MOS場效應管中的內在二極體仍然會形成一條從輸出端到Vcc的電流通路(為了簡化,圖5中沒有畫出該二極體)。因此這種電路不能接高於Vcc的電壓。

圖5 biCMOS輸出電路

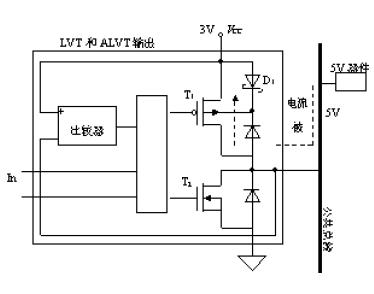

對圖5電路所加的保護電路,如圖6所示。增加了反向偏置的肖特基二極體D1,用以防止電流從輸出端流到Vcc。為了簡化,圖中沒有畫出雙極晶體管。圖6中的輸出端與5V驅動器共用一條匯流排。在三態方式時,電路可以得到保護。當出現匯流排爭奪即兩個驅動器部以高電平驅動匯流排時,比較器將P溝道MOS場效應管T1斷開。當3V器件處於等待方式而3V電源為0時,比較器和肖特基二極體D1可以起保護作用。

圖6用比較器和反向偏置的肖特基二極體保護3V器件的輸出端

4 3V、5V混合系統中不同電平器件介面的4種情況

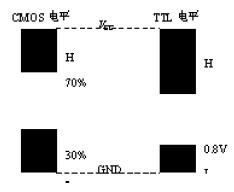

為了保證在混合電壓系統中數據交換的可靠性,必須滿足輸入轉換電平的要求,但又不能超過輸入電壓的限度。圖7就是各種轉換電平的例子:

TTL電平輸入高電平VIH 2V以上

輸入低電平VIL 0.8V以下。

CMOS電平VIH為0.7×Vcc以上

VIL為0.3×Vcc以下。

圖7 TTL及CMOS器件的轉換電平

例如Vcc為5V±0.5V的系統,CMOS的輸入電壓VIH至少是3.85V,而VIL必須小於1.35V。在3V/5V混合系統的設計中,必須討論以下4種信號電平的配置

(1)通常,5V TTL器件可以驅動3V TTL輸入,因為典型雙極晶體管的輸出並不能達到電源電壓幅度。當一個5V器件的輸出為高電平時,內部壓降限制了輸出電壓。典型情況是Vcc-2VBE,即約3.6V。這樣工作通常不會引起5V電源的電流流向3V電源。但是,因為驅動器結構會有所不同,因此必須控制驅動器的輸出不宜超過3.6V以防萬一。

(2)用3V器件驅動5V TTL的輸入端應當是沒有困難的。不管是CMOS或biCMOS器件,3V器件實際上能輸出3V擺幅的電壓。對5V TTL輸入的高電平2V門限是容易滿足的。

(3)當用5V CMOS器件來驅動3V TTL輸入時,必須小心選擇。要選用的3V接收器件應具有5V的容限。

(4)前面曾談到3V輸出可以驅動5V TTL器件輸入,但要注意對5V CMOS器件的輸入來說情況卻大不一樣。應該記住3V輸出是不能可靠地驅動5V CMOS輸入的。在最壞的情況下,當Vcc=5.5V時所要求的VIH至少是3.85V,而3V器件是不能達到的。

5 兩種電平移位器件

上面討論了不同電平器件介面的4種情況,那麼對於第4種情況該怎麼辦?這裡介紹兩種電平移位器件可以解決類似問題。

(1)雙電源電平移位器74LVC4245

74LVC4245是一種雙電源的電平移位器,如圖8所示。5V端用5V電源作為Vcc,而3V端則用3V作為Vcc。它的功能類似於常用的收發器74LVC245,所不同的是用兩個電源而不是一個電源。

74LVC4245的電平移位在其內部進行。雙電源能保證兩邊埠的輸出擺幅部能達到滿電源幅值,並且有很好的雜訊抑制性能。因此該器件用來驅動5V CMOS器件的輸入是很理想的。它的缺點是增加了功耗。

圖8 74LVC4245電平移位器

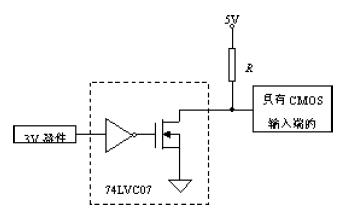

較為簡單的一種電平移位器件是74LVC07。它使用一個漏極開路緩衝器去驅動5V CMOS器件的輸入,如圖9所示。它的輸出端由一個上拉電阻R接到5V電源。

圖9 74LVC07電平移位器

6 結論

5V器件能和3V甚至更低電壓的器件共存於一個系統中。這種情況已經存在並將存在相當長的時間。在設計這種系統時要分析其中邏輯器件的介面問題。其關鍵是理解和運用以上討論的基本概念以保證所設計的電路在不同電壓器件間數據傳輸的可靠性。

[admin via 研發互助社區 ] 3V與5V混合系統中邏輯器介面問題已經有5057次圍觀

http://cocdig.com/docs/show-post-44708.html