1、邏輯電平簡介

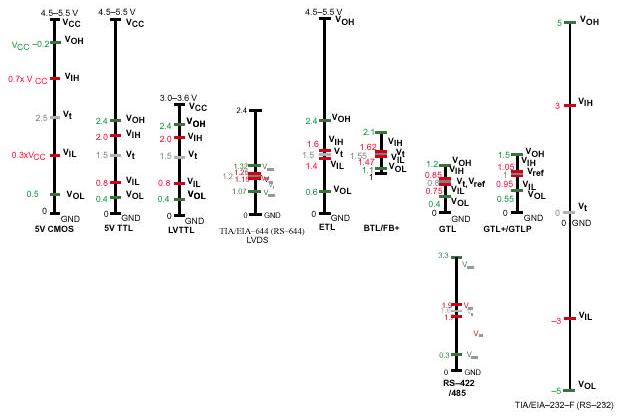

邏輯電平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。

TTL:Transistor-Transistor Logic

CMOS:Complementary Metal Oxide Semicondutor

LVTTL:Low Voltage TTL

LVCMOS:Low Voltage CMOS

ECL:Emitter Coupled Logic,

PECL:Pseudo/Positive Emitter Coupled Logic

LVDS:Low Voltage Differential Signaling

GTL:Gunning Transceiver Logic

BTL: Backplane Transceiver Logic

ETL: enhanced transceiver logic

GTLP:Gunning Transceiver Logic Plus

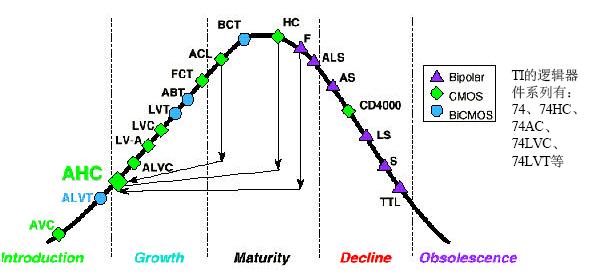

圖1-1:常用邏輯系列器件

S - Schottky Logic

LS - Low-Power Schottky Logic

CD4000 - CMOS Logic 4000

AS - Advanced Schottky Logic

74F - Fast Logic

ALS - Advanced Low-Power Schottky Logic

HC/HCT - High-Speed CMOS Logic

BCT - BiCMOS Technology

AC/ACT - Advanced CMOS Logic

FCT - Fast CMOS Technology

ABT - Advanced BiCMOS Technology

LVT - Low-Voltage BiCMOS Technology

LVC - Low Voltage CMOS Technology

LV - Low-Voltage

CBT - Crossbar Technology

ALVC - Advanced Low-Voltage CMOS Technology

AHC/AHCT - Advanced High-Speed CMOS

CBTLV - Low-Voltage Crossbar Technology

ALVT - Advanced Low-Voltage BiCMOS Technology

AVC - Advanced Very-Low-Voltage CMOS Logic

2、TTL器件和CMOS器件的邏輯電平

2.1:邏輯電平的一些概念

要了解邏輯電平的內容,首先要知道以下幾個概念的含義:

1:輸入高電平(Vih): 保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高於Vih時,則認為輸入電平為高電平。

2:輸入低電平(Vil):保證邏輯門的輸入為低電平時所允許的最大輸入低電平,當輸入電平低於Vil時,則認為輸入電平為低電平。

3:輸出高電平(Voh):保證邏輯門的輸出為高電平時的輸出電平的最小值,邏輯門的輸出為高電平時的電平值都必須大於此Voh。

4:輸出低電平(Vol):保證邏輯門的輸出為低電平時的輸出電平的最大值,邏輯門的輸出為低電平時的電平值都必須小於此Vol。

5:閥值電平(Vt): 數字電路晶元都存在一個閾值電平,就是電路剛剛勉強能翻轉動作時的電平。它是一個界於Vil、Vih之間的電壓值,對於CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩定的輸出,則必須要求輸入高電平> Vih,輸入低電平<Vil,而如果輸入電平在閾值上下,也就是Vil~Vih這個區域,電路的輸出會處於不穩定狀態。

對於一般的邏輯電平,以上參數的關係如下:Voh > Vih > Vt > Vil > Vol。

6:Ioh:邏輯門輸出為高電平時的負載電流(為拉電流)。

7:Iol:邏輯門輸出為低電平時的負載電流(為灌電流)。

8:Iih:邏輯門輸入為高電平時的電流(為灌電流)。

9:Iil:邏輯門輸入為低電平時的電流(為拉電流)。

門電路輸出極在集成單元內不接負載電阻而直接引出作為輸出端,這種形式的門稱為開路門。開路的TTL、CMOS、ECL門分別稱為集電極開路(OC)、漏極開路(OD)、發射極開路(OE),使用時應審查是否接上拉電阻(OC、OD門)或下拉電阻(OE門),以及電阻阻值是否合適。對於集電極開路(OC)門,其上拉電阻阻值RL應滿足下麵條件:

(1):RL < (VCC-Voh)/(n*Ioh+m*Iih)

(2):RL > (VCC-Vol)/(Iol+m*Iil)

其中n:線與的開路門數;m:被驅動的輸入端數。

2.2:常用的邏輯電平

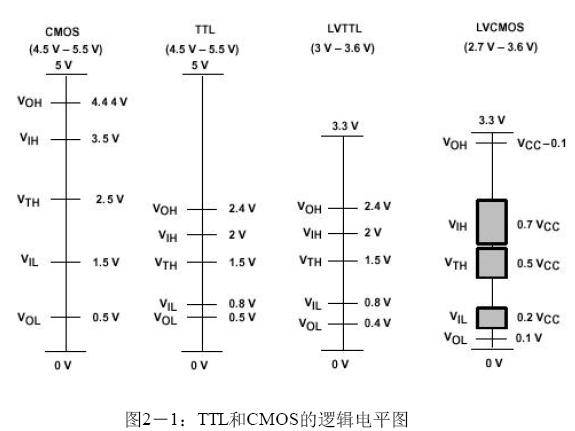

2.3:TTL和CMOS的邏輯電平關係

上圖為5V TTL邏輯電平、5V CMOS邏輯電平、LVTTL邏輯電平和LVCMOS邏輯電平的示意圖。

5V TTL邏輯電平和5V CMOS邏輯電平是很通用的邏輯電平,注意他們的輸入輸出電平差別較大,在互連時要特別注意。

另外5V CMOS器件的邏輯電平參數與供電電壓有一定關係,一般情況下,Voh≥Vcc-0.2V,Vih≥0.7Vcc;Vol≤0.1V,Vil≤0.3Vcc;雜訊容限較TTL電平高。

JEDEC組織在定義3.3V的邏輯電平標準時,定義了LVTTL和LVCMOS邏輯電平標準。LVTTL邏輯電平標準的輸入輸出電平與5V TTL邏輯電平標準的輸入輸出電平很接近,從而給它們之間的互連帶來了方便。 LVTTL邏輯電平定義的工作電壓範圍是3.0-3.6V。

LVCMOS邏輯電平標準是從5V CMOS邏輯電平關注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關,其值如上圖所示。LVCMOS邏輯電平定義的工作電壓範圍是2.7-3.6V。

5V的CMOS邏輯器件工作於3.3V時,其輸入輸出邏輯電平即為LVCMOS邏輯電平,它的Vih大約為0.7×VCC=2.31V左右,由於此電平與LVTTL的Voh(2.4V)之間的電壓差太小,使邏輯器件工作不穩定性增加,所以一般不推薦使用5V CMOS器件工作於3.3V電壓的工作方式。由於相同的原因,使用LVCMOS輸入電平參數的3.3V邏輯器件也很少。

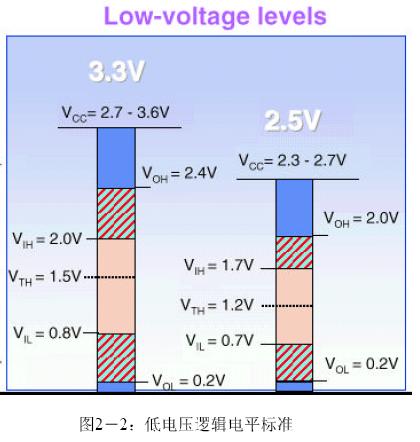

JEDEC組織為了加強在3.3V上各種邏輯器件的互連和3.3V與5V邏輯器件的互連,在參考LVCMOS和LVTTL邏輯電平標準的基礎上,又定義了一種標準,其名稱即為3.3V邏輯電平標準,其參數如下:

從上圖可以看出,3.3V邏輯電平標準的參數其實和LVTTL邏輯電平標準的參數差別不大,只是它定義的Vol可以很低(0.2V),另外,它還定義了其Voh最高可以到VCC-0.2V,所以3.3V邏輯電平標準可以包容LVCMOS的輸出電平。在實際使用當中,對LVTTL標準和3.3V邏輯電平標準並不太區分,某些地方用LVTTL電平標準來替代3.3V邏輯電平標準,一般是可以的。

JEDEC組織還定義了2.5V邏輯電平標準,如上圖所示。另外,還有一種2.5V CMOS邏輯電平標準,它與上圖的2.5V邏輯電平標準差別不大,可兼容。

低電壓的邏輯電平還有1.8V、1.5V、1.2V的邏輯電平。

[admin via 研發互助社區 ] 邏輯電平設計已經有13332次圍觀

http://cocdig.com/docs/show-post-44697.html