非同步複位相比同步複位:

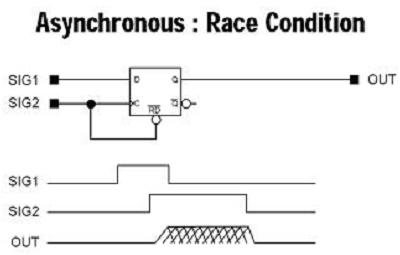

Figure 1 shows an asynchronous race condition where a clock signal is used to reset a flip-flop. When SIG2 is low, the flip-flop is reset to a low state. On the rising edge of SIG2, the designer wants the output to change to the high state of SIG1. Unfortunately, since we don’t know the exact internal timing of the flip-flop or the routing delay of the signal to the clock versus the reset input, we cannot know which signal will arrive first - the clock or the reset. This is a race condition. the clock rising edge appears first, the output will remain low. If the reset signal appears first, the output will go high. A slight change in temperature, voltage, or process may cause an ASIC that works correctly to suddenly work incorrectly.

亞穩態的定義(說明):

在 Howard Johnson 的《High Speed Digital Design: A Handbook of Black Magic》一書中,專門就邏輯電路的亞穩態作了專門的分析。由於 timing margine 不夠,電路的輸入沒有能夠上到所需要的邏輯電平高度,導致邏輯器內部不得不花費額外的時間使得輸出達到所需的穩定邏輯狀態,這個額外的時間,我們也叫作決斷時間(resolution time)。在 Johnson舉的例子里,邏輯器件的邏輯電平是用電容來維持的,如果時序不夠,就好像給電容充電不足。

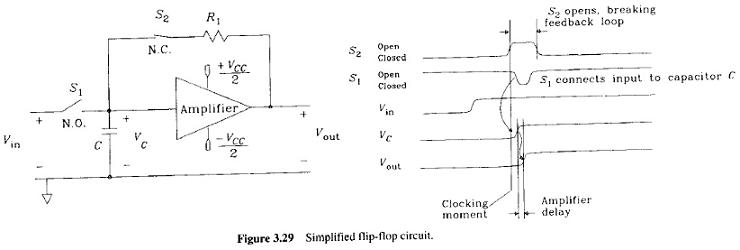

Howard Johnson 在書中(P123 頁-3.11.2)用一個 flip-flop 的例子來說明亞穩態(metastable behavior)。

書中用一個 amplifier,兩個 switch,一個電容來模擬 flip-flop 的工作狀態。電容用來保存電路的邏輯電平,兩個 switch 狀態的改變可以模擬數據的輸入和 flip-flop 的工作狀態。在flip-flop開始翻轉之前,輸入數據的邏輯電平存儲在電容里,然後flip-flop通過一個switch S1斷開與輸入端的連接,同時通過 amplifier(帶有一個正反饋環)開始進行內部的翻轉機制。

從輸入端 switch S1斷開,和正反饋環上的 switch S2閉合開始,amplifier 就處於一個冪指數形式的中間態,或者說是不穩定態(形象地說就是“工作中”),可以用如下式子表達:

V(out)=V(in)exp[kt]。其中 V(in)表示輸入邏輯的電平,V(out)表示輸出的邏輯電平。k 是一個時間常數,它和 amplifier 的帶寬以及正反饋環路有關。

我們看到,如果 flip-flop 在用電容對輸入電壓採樣的時間過短,也就是所謂的時序不夠,就會導致 V(in)的值很小,對於 flip-flop 就需要花很長的時間使得輸出邏輯 V(out)達到標準電平,也就是說電路處於中間態的時間變長,使得電路“反應”變遲鈍。這就是我們所說的“亞穩態”。

從 Johnoson 的一系列試驗可以看出,隨著 timing margine 不足程度的加深,邏輯電路“反應”會越來越慢,當超過一定的極限時候,邏輯電路就沒有輸出。

可以說,電路亞穩態的存在,會給時序設計帶來很多連鎖反應。因此,對於高速邏輯電路的設計,充分的 timing margine 是必需的。

以上是個人的一點體會心得,相關的理論分析和實例可以參閱 Howard Johnson的書。

亞穩態在設計中的問題分析

1. 亞穩態與設計可靠性

設計數字電路時大家都知道同步是非常重要的,特別當要輸入一個信號到一個同步電路中,但是該信號由另一個時鐘驅動時,這是要在介面處採取一些措施,使輸入的非同步信號同步化,否則電路將無法正常工作,因為輸入端很可能出現亞穩態(Metastability),導致採樣錯誤。這裡我們對亞穩態的起因、危害、對可靠性的影響和消除模擬做一些介紹。

2. 亞穩態發生的原因

在同步系統中,如果觸發器的 setup time / hold time 不滿足,就可能產生亞穩態,此時觸發器輸出端 Q 在有效時鐘沿之後比較長的一段時間處於不確定的狀態,在這段時間裡 Q 端會出現毛刺、振蕩、或固定在某一電壓值,而不一定等於數據輸入端 D 的值。這段之間稱為決斷時間(resolution time)。經過 resolution time 之後 Q端將穩定到 0 或1上,但是究竟是0 還是 1,這是隨機的,與輸入沒有必然的關係。亞穩態實質是介於”0””1”電平之間的一個狀態。亞穩態是 FF的一個固有特性。正常採樣也會有一個亞穩態時間。當建立保持時間滿足時,FF 在經歷採樣、亞穩態后,進入一個正確的狀態。如果建立保持時間不滿足,那麼FF會有一個相當長的亞穩態時間,最後隨機進入一個固定態。

3. 亞穩態的危害

由於輸出在穩定下來之前可能是毛刺、振蕩、固定的某一電壓值,因此亞穩態除了導致邏輯誤判之外,輸出 0~1 之間的中間電壓值還會使下一級產生亞穩態,即導致 meta stability的傳播。邏輯誤判(由於組合邏輯的 race,導致匯流排狀態的不穩定)有可能通過電路的特殊設

計減輕危害(如非同步 FIFO中 Gray碼計數器的作用,一次只變化一位),而亞穩態的傳播則擴大了故障面,難以處理。

4. 亞穩態的簡單解決辦法

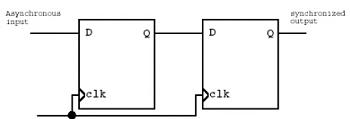

只要系統中有非同步元件,亞穩態就是無法避免的,因此設計的電路首先要減少亞穩態導致錯誤的發生,其次要使系統對產生的錯誤不敏感。前者要靠同步來實現,而後者根據不同的設計應用有不同的處理辦法。用同步來減少亞穩態發生機會的典型電路如圖 1 所示。

圖 1 兩級同步化電路

在圖 1 中,左邊為非同步輸入端,經過兩級觸發器同步,在右邊的輸出將是同步的,而且該輸出基本不存在亞穩態。其原理是即使第一個觸發器的輸出端存在亞穩態,經過一個 CLK 周期后,第二個觸發器 D 端的電平仍未穩定的概率非常小,因此第二個觸發器 Q 端基本不會產生亞穩態。

注意,這裡說的是“基本”,也就是無法“根除”,那麼如果第二個觸發器 Q出現了亞穩態會有什麼後果呢?後果的嚴重程度是由你的設計決定的,如果系統對產生的錯誤不敏感,那麼系統可能正常工作,或者經過短暫的異常之後可以恢復正常工作,例如設計非同步 FIFO時使用格雷碼計數器當讀寫地址的指針就是處於這方面的考慮。如果設計上沒有考慮如何降低系統對亞穩態的敏感程度,那麼一旦出現亞穩態,系統可能就崩潰了。

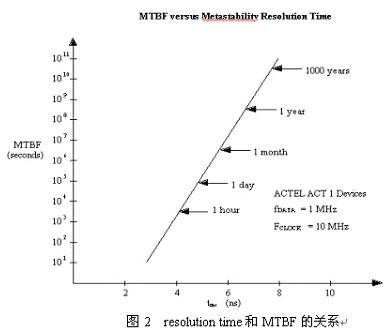

5. 亞穩態與系統可靠性

使用同步電路以後,亞穩態仍然有發生的可能,與此相連的是平均故障間隔時間MTBF(mean time between failure),亞穩態的發生概率與時鐘頻率無關,但是 MTBF與時鐘有密切關係。 有文章提供了一個例子,某一系統在 20MHz 時鐘下工作時,MTBF約為 50年,但是時鐘頻率提高到 40MHz 時,MTBF 只有 1 分鐘!可見降低時鐘頻率可以大大減小亞穩態導致系統錯誤的出現,其原因在於,時鐘周期如果儘可能的大於 resolution time 可減小亞穩態傳遞到下一級的機會,提高系統的 MTBF,如圖 2 所示。

6. 總結

亞穩態與設計可靠性有非常密切的關係,當前對很多設計來說,實現需要的功能並不困難,難的是提高系統的穩定性、可靠性,較小亞穩態發生的概率,並降低系統對亞穩態錯誤的敏感程度可以提高系統的可靠性。

7. Cures for metastability(摘自 johnson 所書)

減少亞穩態出現的關鍵是器件使用比較好的工藝和時鐘周期的余量大一些。好器件工藝的 resolution time會比較短,例如傳統的 TTL 電路中,高速的 74F系列就比74LS好;時鐘頻率低一些,出現亞穩態時提供給輸出穩定的時間也會多一些,這樣可以減小亞穩態傳播的機會。同步系統也存在亞穩態,但是相比非同步系統來說,比較容易控制,只要 setup/hold time滿足就可以,而對非同步系統,這個簡單的要求也不容易滿足,這也是同步系統的優點之一。

問題解答:

處理非同步輸入時,可以使用 2級同步電路,為什麼不用 3級或更多級別的電路呢?

答:2級從理論或實際使用都表明有足夠的可靠性了,所以 3級沒有必要。

解釋為什麼第二個觸發器 D端的電平仍未穩定的概率非常小:

如果一個時鐘周期>resolution time,即:使上一級寄存器有足夠的時間擺脫亞穩態(滿足了建立時間要求),但如果上一級 DFF 採樣錯誤,那麼下級 DFF 同樣繼承這個採樣錯誤值,只是不會出現亞穩態,杜絕了亞穩態的傳遞。如果要穩定的正確採樣,必須引入高速時鐘,

時鐘頻率為原數據頻率的 3 倍以上,根據奈奎斯特採樣定理需要兩倍。

[admin via 研發互助社區 ] 同步與非同步複位,以及相關的亞穩態狀況與設計可靠性已經有19963次圍觀

http://cocdig.com/docs/show-post-43253.html